Для инверсии сигнала данных можно использовать любой вентиль инвертора логики из серии LVC, AHC, AUP. Последняя при питании не выше 3,3В. Например 74LVC1G04.

На задержку да, в принципе можно забить. Но для лучшего вычитания помех желательно сделать дифференциальную линию данных, чтобы фронты прямого и инверсного сигналов DATA примерно совпадали.

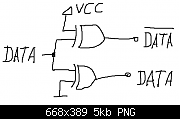

Для этого, например, можно использовать сдвоенный XOR вентиль (типа 74LVC2G86), включенные по схеме:

Да, сигнал принимает от ЦФ, но не каждый ЦФ выдает сигнал для деглитчера. Если не выдает, то этот сигнал можно сделать из сигнала WCK (он же LATCH).

Можно замыкать прямо токовый выход ЦАП, но я такой вариант не пробовал.

Чтобы не заниматься НИОКР, лучше всего использовать проверенную схему УВХ с ветки про 58, только ее можно упростить - использовать обычное однополярное питание ключей.

Для каскада ИУ при этом достаточно использовать ОУ встроенные внутри 1865.

И при использовании УВХ диф. включение 1865 уже не требуется. Либо использовать стандартное включение, либо просто спараллеливание с суммированием сигналов на УВХ.

Разница есть. Чем выше частота, тем меньше "ступенек" в сигнале и хуже видно нелинейности. Поэтому лучше частоту задавать пониже, можно даже меньше килогерца.

Ответить с цитированием

Ответить с цитированием

Социальные закладки