Последний раз редактировалось demon_rt; 08.11.2018 в 10:17.

Если посмотреть на распиновку то как раз понятно. У одних совмещенные вводы DSD и PCM, у других раздельные.

---------- Сообщение добавлено 09:52 ---------- Предыдущее сообщение было 09:50 ----------

Графики есть в даташитах кажется? Я на первыхй взгляд вижу 0 отличий.

Diatonica v.20 - Settima v.3a - Beyerdynamic T1/Audeze LCD-X

Diatonica v.20 - Rotel Ra-935BX - Kef Q7

https://perfectaudio.su/

И че с того, что PCM и DSD входы раздельные? У некоторых АК тоже раздельные или совмещенны, на выбор. И разницы нет.

Это замеры без режектора? Что-то подозрительно хорошо.

А какой там чип АЦП? И на сколько ослабляли входной уровень? Шумовая полка на спектре от АЦП, или это уже ЦАП добавляет?

Не, не в смысле наращивания мощности (ее как раз можно и урезать), а в смысле оптимизации. Чтобы выполнять то же самое плисиной меньшей мощности, и вообще - перенести ее на плату ЦАПов.

Без, но естественно сам дельта-сигма АЦП подфильтровывает, в идеале надо измерения проводить инструментальным АЦП.

Как есть

AK5385A

Немного ЦАП добавил

---------- Сообщение добавлено 15:20 ---------- Предыдущее сообщение было 15:07 ----------

Чудес не бывает, у меня сейчас задействовано 11 DSP на каждый фильтр, всего их 16 на два канала, итого 176 DSP блоков, на частоте обработки 100 МГц.

Оптимизация:

1 - Уменьшение числа отводов фильтров с ухудшением их параметров - не вариант

2 - Уменьшение количества фильтров, не делать мультиплексирование в зависимости от Fs (к примеру оставить один х8, как PCM1794) - результат передескретезация на высоких Fs 192000KHz * 8 = 1.536 MHz - искажения до 0,0015% (отсюда у многих нелюбовь к PCM1794 на высоких Fs)

3 - Повышение частоты обработки (до 200-250 МГц), тем самым выполнить те-же операции на меньшем количестве DSP - результат нагрев ПЛИС до 80 градусов, нафиг такую печку.

---------- Сообщение добавлено 15:26 ---------- Предыдущее сообщение было 15:20 ----------

Итого имеем ПЛИС:

Spartan XC7S100 - 160 DSP не лезет

Artix XC7A75T - 180 DSP лезет но с таким малым запасом трассировать проект с хорошими временными задержками маловероятно.

Artix XC7A100T 240 DSP уже похоже на правду.

"Замполит, чайку?"(с)"Охота за Красным Октябрем".

"Да мне-то что, меняйтесь!"(с)анек.

<-- http://altor1.narod.ru --> Вопросы - в личку, е-мейл, скайп.

Так у меня аттенюатор на реле, дюбой уровень выставить можно, измерения проводились в районе 2V RMS

---------- Сообщение добавлено 15:35 ---------- Предыдущее сообщение было 15:33 ----------

Да

---------- Сообщение добавлено 15:36 ---------- Предыдущее сообщение было 15:35 ----------

Не заметил на LTC2378-20

Дело не в напряжении, а в уровне на входе самого АЦП, относительно его полного диапазона (0dBFS). У большинства АЦП выше -10-15dBFS сильно растут 2 и 3-я гармоники (а у некоторых и выше -30dBFS).

Поэтому вырезают режектором основную гармонику (т.к. именно она идет с большим уровнем), и смотрят только сами гармоники, которые с малым уровнем. Частенько при этом из еще на 20дБ усиливают.

Измерять "прямым методом"(т.е. без режектора) искажения ниже 0.0001% уже тяжело.

---------- Сообщение добавлено 13:49 ---------- Предыдущее сообщение было 13:46 ----------

ТАк там 20 бит всего, а на LTC2380-24 видно.

"Замполит, чайку?"(с)"Охота за Красным Октябрем".

"Да мне-то что, меняйтесь!"(с)анек.

<-- http://altor1.narod.ru --> Вопросы - в личку, е-мейл, скайп.

Спасибо, методика понятна. Вот у меня в пределах 0,0001 и получилось.

---------- Сообщение добавлено 16:24 ---------- Предыдущее сообщение было 16:22 ----------

Работал именно с LTC2378-20. У него очень приличный спектр. На днях хочу им обмерять попробовать в полосе 500 КГц. Так там сразу все нюансы по ВЧ видны, и как ЦФ работает.

---------- Сообщение добавлено 18.10.2018 в 12:42 ---------- Предыдущее сообщение было 17.10.2018 в 16:24 ----------

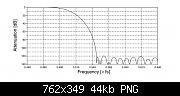

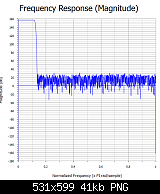

Люди в ЛС спрашивают, чем отличается ЦФ на FPGA от того же SM5847 Пример для х8

SM5847

FPGA DSP FIR

Понятно, спасибо.

Чудеса для этого не требуются. Просто нужно использовать другой подход к проектированию ЦФ:

В частности, можно применить каскадирование. Т.е. выполнять апсемплинг х2 каскадами, тапов потребуется гораздо меньше. Можно само арифметическое ядро сделать универсальным, под любое число каскадов и любые ЧД, вместо кучи отдельных фильтров. Можно оптимизировать саму арифметику, используя полуполосность и симметричность ИХ фазолинейного фильтра. Тогда для мощного ЦФ вполне хватит гораздо более скромной плисины, типа max10 10m04 или lattice LcmXO2-2000. Ну а если не гнаться за супермощностью ЦФ, то можно и в LcmXO2-1200 вписаться.

Очень интересно. Я тоже на SAR-ы от LT периодически поглядываю. Но судя по ДШ, там выше нескольких кГц резко начинают расти искажения. Как оно будет выглядеть в реале - весьма любопытно. Хочется надеятся, что они стоят своих денег, касательно применения на аудиочастотах.

---------- Сообщение добавлено 13:22 ---------- Предыдущее сообщение было 13:19 ----------

Offтопик:

На самом деле выполнима, и даже микруха подходящая для переходника есть

https://www.digikey.com/products/en/...=1&pageSize=25

Это чисто вопрос трудоемкости реализации.

Сумарно выйдет так же как и один.

Если отказаться от IPCore FIR предоставляемых производителем, в частности Xilinx, можно внушительно оптимизировать фильтры, но трудозатраты на реализацию вырастут несоизмеримо, так как придется применять низкоуровневое программирование, оперируя элементами DSP и RAM, и реализуя математический аппарат самостоятельно.

---------- Сообщение добавлено 15:38 ---------- Предыдущее сообщение было 15:28 ----------

Данная микросхема имеет всго лишь 1,2 тысячи LUT, а аппаратных арифметических блоков (DSP) не имеет вообще. На чем сумматоры и умножители делать на логике????

Подчиненный перед лицом начальствующим должен иметь вид лихой и придурковатый, дабы разумением своим не смущать начальство.

Указ Петра I от 09.12.1709:

Если ставить 5842, то лучше непосредственно на аналоговый модуль. В этом случае базовая плата, как таковая вообще не нужна. У меня ПЛИС вынесена на несущую плату, так как она управляет всем, от обработки ручки энкодера до приема данных по USB /SPDIF, фильтрации и отображения информации на экран. И греется она несоизмеримо с 5842.

Да возможно. В голову приходит пропускание данных от обеих каналов через один и тот же фильтр с временным разделением. Тем самым ресурсы экономим в два раза.

Ох не оптимальное это дело, при чем существенно снижается частота обработки по сравнению с DSP. Ну если хочется совсем сэкономить то можно

Но нужно быть готовым, что по логическим ресурсам это будет весьма затратно и большого количества отводов не получить.

Не совсем понял, о чем речь. DSP - это условное название модуля. Какая у него частота умножений - зависит от его устройства. И какая частота умножений на логике - зависит от того как реализуете. Может быть и больше, чем на DSP блоках.

Смотря как придумаете. Я в своем ЦФ делал общее арифметическое ядро, и общий блок памяти на каждый канал. Т.е. все х2 каскады обсчитываются одним и тем же ядром (маком). Все данные читаются и пишутся в один и тот же блок памяти (по разным адресам). Будь то х2 или х32. Т.е. там как таковых мультиплексоров или отводов нет вообще.

Частота на которой работает DSP ПЛИС (я использую именно ПЛИС) зависит от семейства, у xilinx это Spartan, Artix, Kintex, Virtex.

Ошибаетесь. DSP работают на частоте до 500МГц, без проблем, они для этого собственно и интегрированы в ПЛИС. Логика же уже при 300 МГц испытывает большие проблемы верефикации времменных параметров, а на 500 она просто не работает.

---------- Сообщение добавлено 00:23 ---------- Предыдущее сообщение было 00:16 ----------

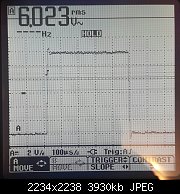

И последние новости по проекту. В ПЛИС реализована функция генерации меандра. Теперь можно тестить усилки))

Ну и вот, что имеем на выходе

Уточняю, что все измерения указанные в топике и меандр включительно проводились не непосредственно с выхода ЦАП, а после аттенюатора на реле и буфера на LM49600.

Социальные закладки