# Features

- General features:

- 4-channel BTL digital Class-D amplifier controller with digital inputs

- 8 differential low-latency ADCs with a 115 dB dynamic range

- 8 programmable digital loop-filter slices

- 8 CMOS level PWM outputs, configurable as 4 BTL channels

- Feedback loop possible after the output filter, across the loudspeaker nodes

- Configurable interconnections between slices and ADCs for versatility and MIMO control

- Volume control and soft mute

- Dynamic loop control with programmable ramp enabling pop-free mode transitions

- Serial audio input / output

- I2S / TDM Serial Audio Interface with 16 downstream and 8 upstream channels

- Input sample rate: 32 to 768 kHz

- 16 to 32-bit supported audio formats

- Control interface

- SPI

- fast mode I<sup>2</sup>C control interface with selectable address for multi-chip systems

# **Applications**

- Streaming audio amplifier solutions

- TV Sound-bars, audio entertainment solutions

- Active loudspeakers

- High performance DAC solutions

- High-resolution low-latency ADC solutions

# **General description**

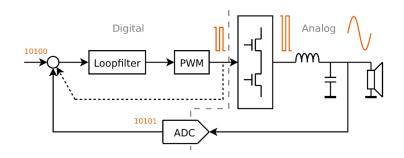

The AX5689 is a 4-channel BTL audio amplifier controller IC with digital inputs and CMOS level PWM outputs. It enables high order digital control loops, with feedback after Class-D output filters.

Embedded low-latency ADCs are used to close the loop behind the output filter in the digital domain. The digital control loop has a high loop gain for all audio frequencies. The AX5689 suppresses all errors caused by the power supply, power stage and output filter within the audio band (20 Hz - 20 kHz). The AX5689 reaches superb performance levels while enabling cost down options.

The low-latency ADCs, PWM outputs and programmable interconnects allow custom configurations, like analog audio inputs / analog line outputs, power supply control, current sensing, temperature sensing, etc.

The AX5689 is compatible with power stages from various vendors and can read and respond to power stage diagnostic signals. The maximum output power is dependent on the user application and is scalable with the number of channels, selected power stages, loads and supply.

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

# Table of Contents

| 1   | Blo | ock diagram                          | 3   |

|-----|-----|--------------------------------------|-----|

| 2   | Pir | nning information                    | 4   |

| 2.1 |     | Pinning                              | 4   |

| 2.2 | -   | Pin description                      | 5   |

| 3   | Ab  | solute maximum ratings               | 7   |

| 4   | Re  | commended operating conditions       | 8   |

| 5   | Th  | ermal characteristics                | 9   |

| 6   | Ch  | aracteristics                        | .10 |

| 6.1 |     | Control interface                    | .13 |

| 6.2 |     | Serial data receiver                 | .16 |

| 6.3 |     | Serial data transmitter              | .17 |

| 6.4 | Ļ   | JTAG Interface                       | .18 |

| 6.5 |     | Clock and reset requirements         | .19 |

| 7   | Fu  | nctional description                 | .20 |

| 7.1 |     | Overview                             | .20 |

| 7.2 |     | Control interface                    | .21 |

| 7.3 |     | Serial audio Interface               | .23 |

| 7.4 | Ļ   | Feed-in filter                       | .24 |

| 7.5 |     | Loop filter                          | .26 |

| 7.6 | ,   | Butterfly mixer                      | .26 |

| 7.7 | ,   | Pulse Width Modulator (PWM)          | .28 |

| 7.8 | 5   | Output crossbar                      | .30 |

| 7.9 | )   | Low-latency ADC (LLADC)              | .31 |

| 7.1 | 0   | Power stage control                  | .34 |

| 7.1 | 1   | Mode control                         | .35 |

| 7.1 | 2   | Startup and shutdown                 | .37 |

| 8   | Re  | gister map                           | .38 |

| 8.1 |     | Bank 0 – Programming mode registers  | .38 |

| 8.2 |     | Bank 0 – Sub-system enable registers | .39 |

|     |     |                                      |     |

| 8.3    | Bank 0 – Volume/ramp generator control           |

|--------|--------------------------------------------------|

| regist | ters42                                           |

| 8.4    | Bank 0 – Serial data transmitter registers45     |

| 8.5    | Bank 0 – Serial data receiver registers47        |

| 8.6    | Bank 0 – Butterfly mixer configuration           |

| regist | ters49                                           |

| 8.7    | Bank 0 – Refgen ADC configuration register<br>52 |

| 8.8    | Bank 0 – Output crossbar configuration           |

| regist | ters                                             |

| 8.9    | Bank 0 – Power stage control registers58         |

| 8.10   | Bank 0 – Status registers60                      |

| 8.11   | Bank 0 – Revision status registers63             |

| 8.12   | Bank 1 – Feed-in configuration registers63       |

| 8.13   | Bank 1 – Loop filter configuration registers.66  |

| 8.14   | Bank 1 – PWM configuration registers73           |

| 8.15   | Bank 1 – LLADC configuration registers75         |

| 9 O    | rdering information76                            |

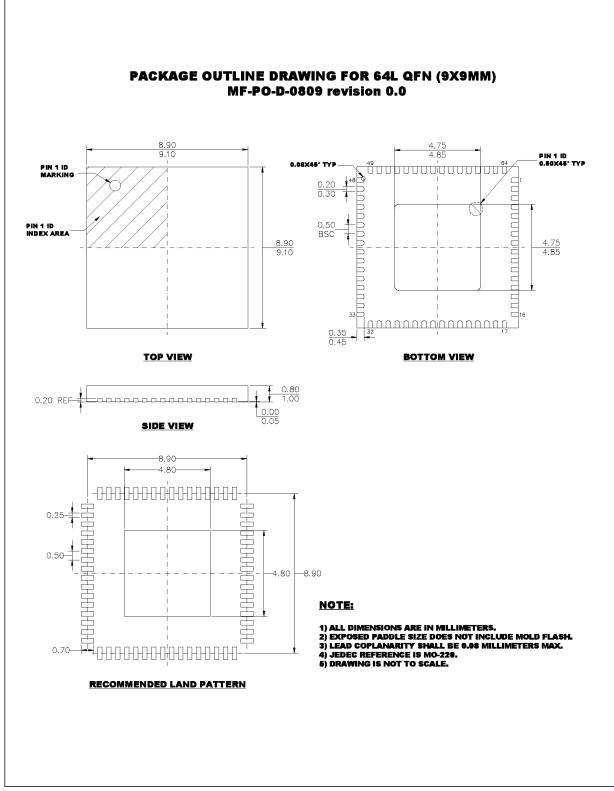

| 10 Pa  | ackage outline AX5689GRK77                       |

| 12 Re  | evision history78                                |

Digital Audio Converter and Amplifier Controller

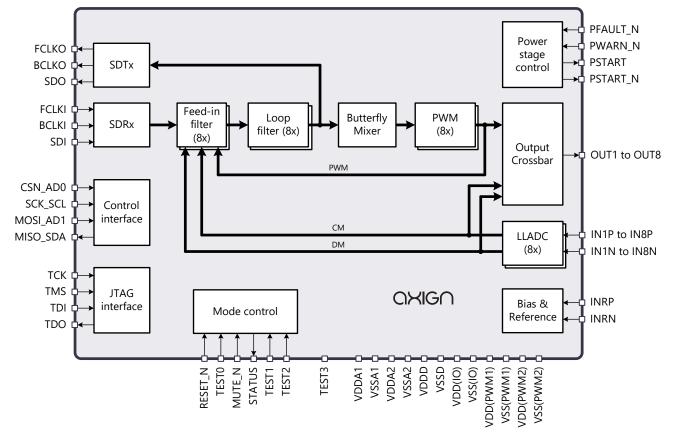

# 1 Block diagram

Figure 1. Block diagram AX5689

Digital Audio Converter and Amplifier Controller

# 2 Pinning information

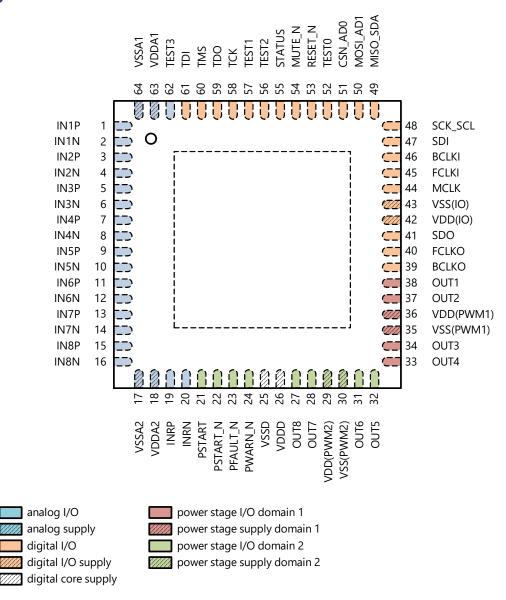

## 2.1 Pinning

Figure 2. AX5689 top view

## 2.2 Pin description

| Pin | Pin descripti<br>Symbol | Type <sup>[1]</sup> | Description                                      |

|-----|-------------------------|---------------------|--------------------------------------------------|

| 1   | IN1P                    | AI                  | analog input for ADC1, terminal P                |

| 2   | IN1N                    | AI                  | analog input for ADC1, terminal N                |

| 3   | IN2P                    | AI                  | analog input for ADC2, terminal P                |

| 4   | IN2N                    | AI                  | analog input for ADC2, terminal N                |

| 5   | IN3P                    | AI                  | analog input for ADC3, terminal P                |

| 6   | IN3N                    | AI                  | analog input for ADC3, terminal N                |

| 7   | IN4P                    | AI                  | analog input for ADC4, terminal P                |

| 8   | IN4N                    | AI                  | analog input for ADC4, terminal N                |

| 9   | IN5P                    | AI                  | analog input for ADC5, terminal P                |

| 10  | IN5N                    | AI                  | analog input for ADC5, terminal N                |

| 11  | IN6P                    | AI                  | analog input for ADC6, terminal P                |

| 12  | IN6N                    | Al                  | analog input for ADC6, terminal N                |

| 13  | IN7P                    | AI                  | analog input for ADC7, terminal P                |

| 14  | IN7N                    | AI                  | analog input for ADC7, terminal N                |

| 15  | IN8P                    | AI                  | analog input for ADC8, terminal P                |

| 16  | IN8N                    | AI                  | analog input for ADC8, terminal N                |

| 17  | VSSA2                   | Р                   | analog ground                                    |

| 18  | VDDA2                   | Р                   | 1.2 V analog supply                              |

| 19  | INRP                    | AI                  | input for reference ADC, terminal P              |

| 20  | INRN                    | AI                  | input for reference ADC, terminal N              |

| 21  | PSTART                  | DO                  | start-up power stage, active high <sup>(2)</sup> |

| 22  | PSTART_N                | DIO                 | start-up power stage, active low <sup>(2)</sup>  |

| 23  | PFAULT_N                | DI                  | output stage fault detection, active low         |

| 24  | PWARN_N                 | DI                  | output stage warning detection, active low       |

| 25  | VSSD                    | Р                   | digital ground                                   |

| 26  | VDDD                    | Р                   | 1.2 V digital supply                             |

| 27  | OUT8                    | DO                  | data (PWM) for channel 8                         |

| 28  | OUT7                    | DO                  | data (PWM) for channel 7                         |

| 29  | VDD(PWM2)               | Р                   | 3.3 V supply for PWM outputs                     |

| 30  | VSS(PWM2)               | Р                   | ground for PWM outputs                           |

| 31  | OUT6                    | DO                  | data (PWM) for channel 6                         |

| 32  | OUT5                    | DO                  | data (PWM) for channel 5                         |

| 33  | OUT4                    | DO                  | data (PWM) for channel 4                         |

| 34  | OUT3                    | DO                  | data (PWM) for channel 3                         |

| 35  | VSS(PWM1)               | Р                   | ground for PWM outputs                           |

| 36  | VDD(PWM1)               | Р                   | 3.3 V supply for PWM outputs                     |

| Table 1. | Pin descript | ion                 |                                                                                              |

|----------|--------------|---------------------|----------------------------------------------------------------------------------------------|

| Pin      | Symbol       | Type <sup>[1]</sup> | Description                                                                                  |

| 37       | OUT2         | DO                  | data (PWM) for channel 2                                                                     |

| 38       | OUT1         | DO                  | data (PWM) for channel 1                                                                     |

| 39       | BCLKO        | DO                  | bit clock for the serial audio data output                                                   |

| 40       | FCLKO        | DO                  | frame clock for the serial audio data output                                                 |

| 41       | SDO          | DO                  | serial audio data output                                                                     |

| 42       | VDD(IO)      | Р                   | 3.3 V IO supply                                                                              |

| 43       | VSS(IO)      | Р                   | IO ground                                                                                    |

| 44       | MCLK         | DI                  | master clock input                                                                           |

| 45       | FCLKI        | DI                  | frame clock for the serial audio data input                                                  |

| 46       | BCLKI        | DI                  | bit clock for the serial audio data                                                          |

| 47       | SDI          | DI                  | serial audio data input                                                                      |

| 48       | SCK_SCL      | DI                  | control interface bit clock.                                                                 |

| 49       | MISO_SDA     | DO/DIO              | control interface: data output in SPI mode, bidirectional data line in I <sup>2</sup> C mode |

| 50       | MOSI_AD1     | DI                  | control interface: data input in SPI mode, AD1 address select input in I <sup>2</sup> C mode |

| 51       | CSN_AD0      | DI                  | control interface: chip select in SPI mode, AD0 address select in I <sup>2</sup> C mode      |

| 52       | TEST0        | DI                  | reserved for testing; connect to ground                                                      |

| 53       | RESET_N      | DI                  | global reset input, active low                                                               |

| 54       | MUTE_N       | DI                  | mute: soft mutes when low, unmutes when high                                                 |

| 55       | STATUS       | DO                  | status output (invalid data/settings, power stage fault, etc.)                               |

| 56       | TEST2        | DI                  | reserved for testing; connect to ground                                                      |

| 57       | TEST1        | DI                  | reserved for testing; connect to ground                                                      |

| 58       | ТСК          | DI                  | JTAG interface clock                                                                         |

| 59       | TDO          | DO                  | JTAG data output                                                                             |

| 60       | TMS          | DI                  | JTAG test mode select                                                                        |

| 61       | TDI          | DI                  | JTAG data input                                                                              |

| 62       | TEST3        | AIO                 | reserved for testing; leave floating                                                         |

| 63       | VDDA1        | Р                   | 1.2 V analog supply                                                                          |

| 64       | VSSA1        | Р                   | analog ground                                                                                |

| 65       | EPAD         | Р                   | exposed pad; connect to ground                                                               |

|          |              |                     |                                                                                              |

[1] Type description: P = Power, A = Analog, D = Digital, I = Input, O = Output

# 3 Absolute maximum ratings

#### Table 2. Absolute maximum ratings<sup>[1]</sup>

| Symbol               | Parameter               | Conditions                                                                    | Min   | Max                      | Unit |

|----------------------|-------------------------|-------------------------------------------------------------------------------|-------|--------------------------|------|

| V <sub>DD(IO)</sub>  | I/O supply voltage      | pin VDD(IO); relative to V <sub>SS(IO)</sub> <sup>[2]</sup>                   | -0.3  | 3.63                     | V    |

| V <sub>DD(PWM)</sub> | PWM supply voltage      | pins VDD(PWM1), VDD(PWM2);<br>relative to V <sub>SS(PWM)</sub> <sup>[2]</sup> | -0.3  | 3.63                     | V    |

| V <sub>DDD</sub>     | digital supply voltage  | pin VDDD; relative to $V_{SSD}^{[2]}$                                         | -0.3  | 1.32                     | V    |

| V <sub>DDA</sub>     | analog supply voltage   | pins VDDA1, VDDA2 relative to V <sub>SSA</sub> <sup>[2]</sup>                 | -0.3  | 1.32                     | V    |

| V <sub>in</sub>      | input voltage           | relative to $V_{SSA}$                                                         |       |                          |      |

|                      |                         | pins IN1P to IN8P; pins IN1N to<br>IN8N; pin INRP, pin INRN, pin<br>VREF      | -0.3  | V <sub>DDA</sub> +0.3    | V    |

|                      |                         | relative to V <sub>SS(IO)</sub>                                               | ·     | ·                        |      |

|                      |                         | all other pins                                                                | -0.3  | V <sub>DD(IO)</sub> +0.3 | V    |

| T <sub>stg</sub>     | storage temperature     |                                                                               | -55   | +150                     | °C   |

| T <sub>amb</sub>     | ambient temperature     |                                                                               | -40   | +85                      | °C   |

| V <sub>ESD</sub>     | electrostatic discharge | human body model <sup>[3]</sup>                                               | -2000 | +2000                    | V    |

|                      | voltage                 | charged device model [4]                                                      | -500  | +500                     | V    |

Absolute maximum ratings are stress ratings only. Permanent damage to the devices may be caused by continuously operating at or beyond these limits. Functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions are not implied.

[2] The voltage potential of the power supply grounds V<sub>SSA</sub>, V<sub>SSD</sub>, V<sub>SS(PWM1)</sub>, V<sub>SS(PMW2)</sub> (pins VSSA, VSSD, VSS(IO), VSS(PWM1), VSS(PWM2)) must be within ±0.3 V of each other.

[3] According to JEDEC JS-001 specification.

[4] According to JESD22-C101 specification.

# 4 Recommended operating conditions

#### Table 3. Operating conditions

| Symbol               | Parameter              | Conditions                                               | Min     | Тур | Max    | Unit |

|----------------------|------------------------|----------------------------------------------------------|---------|-----|--------|------|

| V <sub>DD(IO)</sub>  | IO supply voltage      | pin VDD(IO); with respect to $V_{SS(IO)}$                | 3.0     | 3.3 | 3.6    | V    |

| V <sub>DD(PWM)</sub> | PWM out supply range   | pins VDD(PWM1), VDD(PWM2); with respect to $V_{SS(PWM)}$ | 3.0     | 3.3 | 3.6    | V    |

| V <sub>DDD</sub>     | digital supply voltage | pin VDDD; with respect to V <sub>SSD</sub>               | 1.1     | 1.2 | 1.3    | V    |

| V <sub>DDA</sub>     | analog supply voltage  | pins VDDA1, VDDA2; with respect to V <sub>SSA</sub>      | 1.1     | 1.2 | 1.3    | V    |

| f <sub>MCLK</sub>    | MCLK clock frequency   |                                                          | 45.1584 | -   | 49.152 | MHz  |

# **5** Thermal characteristics

#### Table 4. Thermal characteristics

| Symbol          | Parameter                              | Conditions | Тур | Unit |

|-----------------|----------------------------------------|------------|-----|------|

| θ <sub>JA</sub> | Junction to ambient thermal resistance | still air  | 23  | °C/W |

| θ <sub>JC</sub> | Junction to case thermal resistance    |            | 1.6 | °C/W |

# **6** Characteristics

#### Table 5. Characteristics

Operating conditions:  $V_{DDD} = V_{DDA1} = V_{DDA2} = 1.2 V$ ;  $V_{DD(IO)} = V_{DD(PWM1)} = V_{DD(PWM1)} = 3.3 V$ ;  $T_a = +25 °$ C;  $f_{sig} = 1 kHz$ ;  $f_s = 48 kHz$ ; MCLK = 49.152 MHz; 32-bits audio data; unless stated otherwise.

| Symbol               | z; MCLK = 49.152 MHz; 32-bi<br>Parameter             | Conditions                                 | Min | Тур  | Max | Unit |

|----------------------|------------------------------------------------------|--------------------------------------------|-----|------|-----|------|

| Power                | 1                                                    | 1                                          | 1   | I    | I   | I    |

| I <sub>DD(IO)</sub>  | I/O supply current                                   | operating; all channels<br>enabled         | -   | 4.4  | -   | mA   |

|                      |                                                      | power down; reset active and MCLK disabled | -   | 5.8  | 12  | μΑ   |

| IDD(PWM)             | PWM supply current                                   | operating; all channels<br>enabled         | -   | 2.8  | -   | mA   |

|                      |                                                      | power down; reset active and MCLK disabled | -   | 15.8 | 16  | μA   |

| I <sub>DDD</sub>     | digital supply current                               | operating; all channels<br>enabled         | -   | 7.3  | -   | mA   |

|                      |                                                      | power down; reset active and MCLK disabled | -   | 8.2  | 9   | μΑ   |

| I <sub>DDA</sub>     | analog supply current                                | operating; all channels<br>enabled         | -   | 71   | -   | mA   |

|                      |                                                      | power down; reset active and MCLK disabled | -   | 38   | 300 | μΑ   |

| Low laten            | cy ADCs                                              |                                            |     |      | L   | •    |

| l <sub>i(dm)fs</sub> | full-scale differential mode input current           |                                            | -   | 4.81 | -   | mA   |

| I <sub>i(cm)fs</sub> | full-scale common mode input current                 |                                            | -   | 9.28 | -   | mA   |

| I <sub>os(dm)</sub>  | differential mode input<br>equivalent offset current |                                            | -   | 0.45 | -   | μΑ   |

| V <sub>i(cm)</sub>   | common mode input<br>voltage                         |                                            | -   | 0.52 | -   | V    |

| Z <sub>i(dm)</sub>   | differential mode input                              | ADC enabled                                | -   | 2.6  | -   | Ω    |

|                      | impedance                                            | ADC disabled                               | -   | 120  | -   | kΩ   |

| Z <sub>i(cm)</sub>   | common mode input                                    | ADC enabled                                | -   | 1.05 | -   | Ω    |

|                      | impedance                                            | ADC disabled                               | -   | 120  | -   | kΩ   |

| BW <sub>fs</sub>     | full scale bandwidth                                 |                                            | -   | 60   | -   | kHz  |

| DR <sub>dm</sub>     | differential mode<br>dynamic range                   | 20 Hz to 20 kHz; -60 dB<br>input           | 108 | 111  | -   | dB   |

|                      |                                                      | A-weighted; -60 dB input                   | 110 | 113  | -   | dB   |

| DR <sub>cm</sub>     | common mode dynamic                                  | 20 Hz to 20 kHz                            | 80  | 82   | -   | dB   |

|                      | range                                                | A-weighted                                 | 82  | 84   | -   | dB   |

| SNR                  | signal to noise ratio                                | 20 Hz to 20 kHz; -1 dBFS<br>output         | 105 | 111  | -   | dB   |

#### Table 5. Characteristics

Operating conditions:  $V_{DDD} = V_{DDA1} = V_{DDA2} = 1.2 \text{ V}$ ;  $V_{DD(IO)} = V_{DD(PWM1)} = V_{DD(PWM1)} = 3.3 \text{ V}$ ;  $T_a = +25 \text{ °C}$ ;  $f_{sig} = 1 \text{ kHz}$ ;  $f_s = 48 \text{ kHz}$ ; MCLK = 49.152 MHz; 32-bits audio data; unless stated otherwise.

| Symbol            | Parameter                                                             | Conditions                                                                                                                                                                         | Min                     | Тур  | Max                     | Unit  |

|-------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

|                   |                                                                       | A-weighted; -1 dBFS<br>output                                                                                                                                                      | 107                     | 113  | -                       | dB    |

| THD+N             | total harmonic distortion plus noise                                  | 20 Hz to 20 kHz; -1 dBFS<br>output                                                                                                                                                 | -90                     | -100 | -                       | dB    |

| CM2DM             | input equivalent<br>common-mode to<br>differential-mode<br>conversion |                                                                                                                                                                                    | -90                     | -    | -                       | dB    |

| PSR               | power supply rejection                                                | measured with respect to<br>differential mode output;<br>ADC input is open; test<br>signal on $V_{DDA} = 217$ Hz,<br>square wave and<br>broadband noise; $V_r = 66$<br>m $V_{P-P}$ | -100                    | -    | -                       | dBFS  |

| $\alpha_{ct}$     | crosstalk                                                             | between ADC channels;<br>20 Hz to 20 kHz                                                                                                                                           | -120                    | -    | -                       | dB    |

| ∆G <sub>dm</sub>  | differential mode gain<br>mismatch                                    | between devices                                                                                                                                                                    | -0.23                   | -    | +0.23                   | dB    |

|                   |                                                                       | between channels                                                                                                                                                                   | -0.08                   | -    | +0.08                   | dB    |

| $\Delta G_{cm}$   | common mode gain<br>mismatch                                          | between devices                                                                                                                                                                    | -0.25                   | -    | +0.25                   | dB    |

|                   |                                                                       | between channels                                                                                                                                                                   | -0.1                    | -    | +0.1                    | dB    |

| SR                | slew rate                                                             | differential mode                                                                                                                                                                  | -                       | 2.2  | -                       | mA/µs |

|                   |                                                                       | common mode                                                                                                                                                                        | -                       | 14   | -                       | mA/µs |

| Digital inp       | out/output                                                            |                                                                                                                                                                                    |                         |      | L                       |       |

| V <sub>IL</sub>   | LOW-level input voltage                                               |                                                                                                                                                                                    | 0                       | -    | $0.3 \times V_{DD(IO)}$ | V     |

| VIH               | High-level input voltage                                              |                                                                                                                                                                                    | $0.7 \times V_{DD(IO)}$ | -    | V <sub>DD(IO)</sub>     | V     |

| I <sub>L(I)</sub> | input leakage current                                                 | V <sub>1</sub> = 3.3 V or 0 V                                                                                                                                                      | -1                      | -    | 1                       | μA    |

| I <sub>L(O)</sub> | output leakage current                                                | tristate output; $V_0 = 3.3 V$ or 0 V                                                                                                                                              | -                       | -    | ±10                     | μA    |

| C <sub>i</sub>    | input capacitance                                                     |                                                                                                                                                                                    | -                       | -    | 2.5                     | pF    |

| I <sub>OL</sub>   | LOW-level output current                                              | V <sub>OL</sub> = 0.4 V; pins FCLKO,<br>BCLKO, SDO, OUT1,<br>OUT2, OUT3, OUT4,<br>OUT5, OUT6, OUT7, OUT8                                                                           | 13.9                    | -    | -                       | mA    |

|                   |                                                                       | V <sub>OL</sub> = 0.4 V; all other<br>digital output pins                                                                                                                          | 7.0                     | -    | -                       | mA    |

| I <sub>OH</sub>   | HIGH-level output<br>current                                          | $V_{OH} = V_{DD(IO)} - 0.4 V; pins$<br>FCLKO, BCLKO, SDO,<br>OUT1, OUT2, OUT3,<br>OUT4, OUT5, OUT6,<br>OUT7, OUT8                                                                  | 9.8                     | -    | -                       | mA    |

#### Table 5. Characteristics

Operating conditions:  $V_{DDD} = V_{DDA1} = V_{DDA2} = 1.2 \text{ V}$ ;  $V_{DD(IO)} = V_{DD(PWM1)} = V_{DD(PWM1)} = 3.3 \text{ V}$ ;  $T_a = +25 \text{ °C}$ ;  $f_{sig} = 1 \text{ kHz}$ ;  $f_s = 48 \text{ kHz}$ ; MCLK = 49.152 MHz; 32-bits audio data; unless stated otherwise.

| Symbol               | Parameter                      | Conditions                                                                   | Min | Тур | Max | Unit |

|----------------------|--------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

|                      |                                | $V_{OH} = V_{DD(IO)} - 0.4 \text{ V}; \text{ all}$ other digital output pins | 4.8 | -   | -   | mA   |

| R <sub>pd(int)</sub> | internal pull-down<br>resistor | pin TEST0, RESET_N,<br>MUTE_N, TEST1, TEST2,<br>TCK, TMS, TDI                | 36  | 52  | 85  | kΩ   |

| R <sub>pu(int)</sub> | internal pull-up resistor      | pin PFAULT_N, PWARN_N                                                        | 36  | 54  | 85  | kΩ   |

### 6.1 Control interface

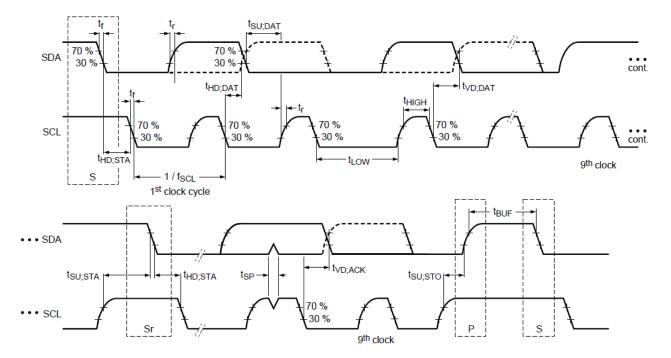

### 6.1.1 I2C interface – slave

#### Table 6.I2C-bus characteristics

| 201/21/      | 2 2 C V A T               | 10 °C + 0F | °C; simulated values         |

|--------------|---------------------------|------------|------------------------------|

| $3UV \leq V$ | $(0) \leq 30 V^{2} I_{a}$ | = -40 + 85 | $1$ $\cdot$ similated values |

| 5.0 . 2 .    | DD(10) = 3.0              | 10 010 000 | e, stinatated values         |

| Symbol               | Parameter                                        | Condition                                             | Min | Тур | Мах | Unit |

|----------------------|--------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| $f_{scl}$            | SCL clock frequency                              |                                                       | 0   | -   | 400 | kHz  |

| $t_{\text{HD(STA)}}$ | hold time (repeated) START condition             | After this period, the first clock pulse is generated | 0.6 | -   | -   | μs   |

| t <sub>LOW</sub>     | LOW period of the SCL clock                      |                                                       | 1.3 | -   | -   | μs   |

| t <sub>HIGH</sub>    | HIGH period of the SCL clock                     |                                                       | 0.6 | -   | -   | μs   |

| $t_{\text{SU(STA)}}$ | set-up time for a repeated<br>START condition    |                                                       | 0.6 | -   | -   | μs   |

| t <sub>HD(DAT)</sub> | data hold time                                   |                                                       | 0   | -   | -   | μs   |

| t <sub>su(dat)</sub> | data set-up time                                 |                                                       | 100 | -   | -   | ns   |

| t <sub>r</sub>       | rise time of both SDA and SCL signals            |                                                       | -   | -   | 300 | ns   |

| t <sub>f</sub>       | fall time of both SDA and SCL signals            |                                                       | -   | -   | 300 | ns   |

| $t_{\text{SU(STO)}}$ | set-up time for STOP condition                   |                                                       | 0.6 | -   | -   | μs   |

| t <sub>BUF</sub>     | bus free time between a STOP and START condition |                                                       | 1.3 | -   | -   | μs   |

| C <sub>b</sub>       | capacitive load for each bus line                |                                                       | -   | -   | 400 | pF   |

| t <sub>VD(DAT)</sub> | data valid time                                  |                                                       | -   | -   | 0.9 | μs   |

| t <sub>VD(ACK)</sub> | data valid acknowledge time                      |                                                       | -   | -   | 0.9 | μs   |

# Digital Audio Converter and Amplifier Controller

The input levels of the I2C-bus receiver are with respect to  $V_{DD(IO)}$  and not related to the bus voltage, as required by the I2C-bus specification. If the  $V_{DD(IO)}$  supply of the device is switched off, SDA and SCL pins connected to the I2C-bus are set to a floating condition and do not disturb the I2C-bus lines.

Digital Audio Converter and Amplifier Controller

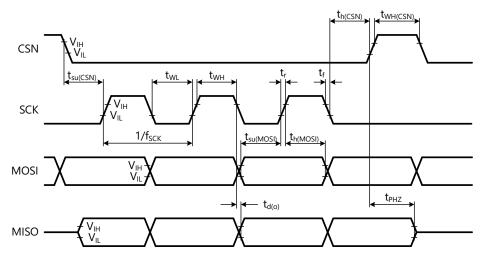

### 6.1.2 SPI Interface – slave

#### Table 7. SPI characteristics

$3.0 V \le V_{DD(IO)} \le 3.6 V$ ;  $T_a = -40 \degree C$  to  $+85 \degree C$ ; simulated values

| Symbol                | Parameter Conditions Min            |                | Тур                     | Max | Unit                    |     |

|-----------------------|-------------------------------------|----------------|-------------------------|-----|-------------------------|-----|

| f <sub>scк</sub>      | SCK clock frequency                 |                | -                       | -   | 10                      | MHz |

| t <sub>WL</sub>       | pulse width LOW                     | pin SCK        | 0.25 / f <sub>SCK</sub> | -   | -                       | ns  |

| t <sub>WH</sub>       | pulse width HIGH                    | pin SCK        | 0.25 / f <sub>SCK</sub> | -   | -                       | ns  |

| t <sub>r</sub>        | rise time                           | pins SCK, MOSI | -                       | -   | 0.17 / f <sub>SCK</sub> | ns  |

| t <sub>f</sub>        | fall time                           | pins SCK, MOSI | -                       | -   | 0.17 / f <sub>SCK</sub> | ns  |

| t <sub>su(CSN)</sub>  | CSN setup time                      |                | 120                     | -   | -                       | ns  |

| t <sub>h(CSN)</sub>   | CSN hold time                       |                | 120                     | -   | -                       | ns  |

| t <sub>WH(CSN)</sub>  | CSN pulse width HIGH                |                | 15                      | -   | -                       | μs  |

| t <sub>su(MOSI)</sub> | MOSI setup time                     |                | 30                      | -   | -                       | ns  |

| t <sub>h(MOSI)</sub>  | MOSI hold time                      |                | 30                      | -   | -                       | ns  |

| t <sub>d(o)</sub>     | output delay time                   | pin MISO       | -                       | -   | 100                     | ns  |

| t <sub>PHZ</sub>      | HIGH to OFF state propagation delay | pin MISO       | -                       | -   | 100                     | ns  |

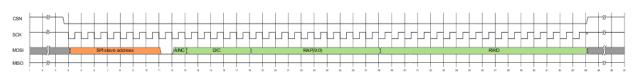

Figure 4. SPI timing characteristics

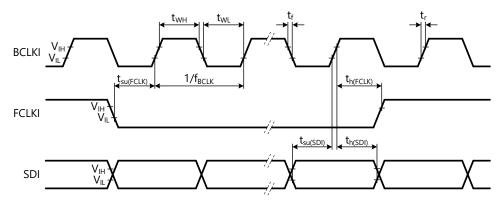

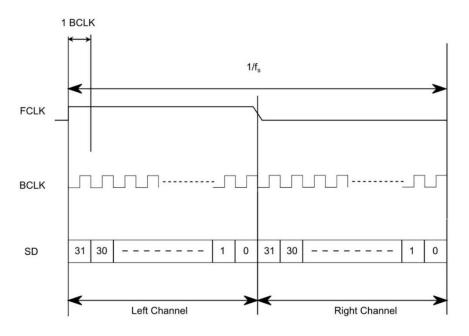

### 6.2 Serial data receiver

### Table 8. Serial data receiver characteristics

$3.0 V \le V_{DD(IO)} \le 3.6 V$ ;  $T_a = -40 \degree C$  to  $+85 \degree C$ ; simulated values.

| Symbol                | Parameter                     | Conditions             | Min                      | Тур | Max                      | Unit |

|-----------------------|-------------------------------|------------------------|--------------------------|-----|--------------------------|------|

| f <sub>FCLK</sub>     | frame clock frequency         | pin FCLKI              | 32                       | -   | 768                      | kHz  |

| f <sub>BCLK</sub>     | bit clock frequency           | pin BCLKI              | $32 \times f_{FCLK}$     | -   | 49.152                   | MHz  |

| t <sub>WH</sub>       | pulse width HIGH              | pin BCLKI              | 0.25 / f <sub>BCLK</sub> | -   | -                        | ns   |

| t <sub>WL</sub>       | pulse width LOW               | pin BCLKI              | 0.25 / f <sub>BCLK</sub> | -   | -                        | ns   |

| t <sub>r</sub>        | rise time                     | pins BCLKI, FCLKI, SDI | -                        | -   | 0.17 / f <sub>BCLK</sub> | ns   |

| t <sub>f</sub>        | fall time                     | pins BCLKI, FCLKI, SDI | -                        | -   | 0.17 / f <sub>BCLK</sub> | ns   |

| t <sub>su(FCLK)</sub> | frame clock input set-up time | pin FCLKI              | 4                        | -   | -                        | ns   |

| t <sub>h(FCLK)</sub>  | frame clock input hold time   | pin FCLKI              | 4                        | -   | -                        | ns   |

| t <sub>su(SDI)</sub>  | serial data input set-up time | pin SDI                | 4                        | -   | -                        | ns   |

| t <sub>h(SDI)</sub>   | serial data input hold time   | pin SDI                | 4                        | -   | -                        | ns   |

Figure 5. Serial data receiver timing characteristics

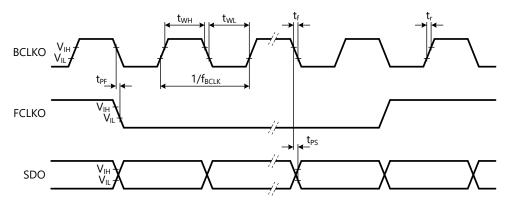

### 6.3 Serial data transmitter

#### Table 9. Serial data transmitter characteristics

$3.0 V \le V_{DD(IO)} \le 3.6 V$ ;  $T_a = -40 \degree$ C to  $+85 \degree$ C; simulated values.

| Symbol            | Parameter                            | Conditions                                       | Min                      | Тур | Max    | Unit |

|-------------------|--------------------------------------|--------------------------------------------------|--------------------------|-----|--------|------|

| f <sub>FCLK</sub> | frame clock frequency                | pin FCLKO                                        | 32                       | -   | 768    | kHz  |

| f <sub>BCLK</sub> | bit clock frequency                  | pin BCLKO                                        | $32 \times f_{FCLK}$     | -   | 49.152 | MHz  |

| t <sub>WH</sub>   | pulse width HIGH                     | pin BCLKO; C <sub>L</sub> = 10 pF                | 0.35 / f <sub>BCLK</sub> | -   | -      | ns   |

| t <sub>WL</sub>   | pulse width LOW                      | pin BCLKO; C <sub>L</sub> = 10 pF                | 0.35 / f <sub>BCLK</sub> | -   | -      | ns   |

| t <sub>r</sub>    | rise time                            | pins BCLKO, FCLKO, SDO;<br>$C_L = 10 \text{ pF}$ | -                        | -   | 2      | ns   |

| t <sub>f</sub>    | fall time                            | pins BCLKO, FCLKO, SDO;<br>$C_L = 10 \text{ pF}$ | -                        | -   | 2      | ns   |

| t <sub>PF</sub>   | frame clock output propagation delay |                                                  | -                        | -   | 5      | ns   |

| t <sub>PS</sub>   | serial data output propagation delay |                                                  | -                        | -   | 5      | ns   |

Figure 6. Serial data transmitter timing characteristics

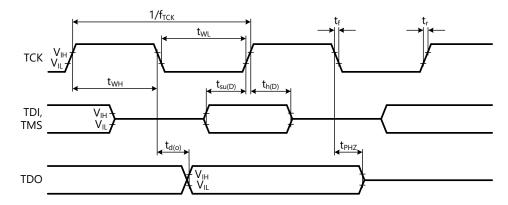

## 6.4 JTAG Interface

#### Table 10. JTAG interface characteristics

3.0 V  $\leq$  V<sub>DD(IO)</sub>  $\leq$  3.6 V; T<sub>a</sub> = -40 °C to +85 °C; simulated values

| Symbol             | Parameter                           | Conditions         | Min                     | Тур | Max                     | Unit |

|--------------------|-------------------------------------|--------------------|-------------------------|-----|-------------------------|------|

| f <sub>TCK</sub>   | TCK clock frequency                 |                    | -                       | -   | 10                      | MHz  |

| t <sub>WL</sub>    | pulse width LOW                     | pin TCK            | 0.25 / f <sub>TCK</sub> | -   | -                       | ns   |

| t <sub>WH</sub>    | pulse width HIGH                    | pin TCK            | 0.25 / f <sub>TCK</sub> | -   | -                       | ns   |

| tr                 | rise time                           | pins TCK, TMS, TDI | -                       | -   | 0.17 / f <sub>тск</sub> | ns   |

| t <sub>f</sub>     | fall time                           | pins TCK, TMS, TDI | -                       | -   | 0.17 / f <sub>TCK</sub> | ns   |

| t <sub>su(D)</sub> | data input set-up time              | pins TDI, TMS      | 5                       | -   | -                       | ns   |

| t <sub>h(D)</sub>  | date input hold time                | pins TDI, TMS      | 5                       | -   | -                       | ns   |

| t <sub>d(o)</sub>  | output delay time                   | pin TDO            | 15                      | -   | -                       | ns   |

| t <sub>PHZ</sub>   | HIGH to OFF state propagation delay | pin TDO            | -                       | -   | 15                      | ns   |

Figure 7. JTAG timing characteristics

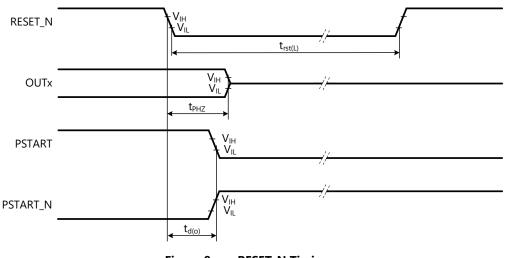

## 6.5 Clock and reset requirements

#### Table 11. Master clock requirements

| Symbol            | Parameter Conditions |          | Min                    | Тур | Max                    | Unit |

|-------------------|----------------------|----------|------------------------|-----|------------------------|------|

| f <sub>MCLK</sub> | MCLK clock frequency |          | 45.1584                | -   | 49.152                 | MHz  |

| t <sub>WL</sub>   | pulse width LOW      | pin MCLK | 0.25/f <sub>MCLK</sub> | -   | -                      | ns   |

| t <sub>WH</sub>   | pulse width HIGH     | pin MCLK | 0.25/f <sub>MCLK</sub> | -   | -                      | ns   |

| t <sub>r</sub>    | rise time            | pin MCLK | -                      | -   | 0.17/f <sub>MCLK</sub> | ns   |

| t <sub>f</sub>    | fall time            | pin MCLK | -                      | -   | 0.17/f <sub>MCLK</sub> | ns   |

[1] The wideband jitter that can be tolerated is approximately 100 ps RMS period jitter (or 600ps peak-to-peak) to keep the dynamic range above 110 dB. Baseband jitter (100 Hz to 200 kHz) must be less than 1.6 ns RMS to keep the dynamic range above 110 dB.

#### Table 12.Reset requirements

| Symbol              | Parameter                           | Conditions                                                | Min                    | Тур | Max                   | Unit |

|---------------------|-------------------------------------|-----------------------------------------------------------|------------------------|-----|-----------------------|------|

| t <sub>rst(L)</sub> | reset LOW time                      |                                                           | 20 / f <sub>MCLK</sub> | -   | -                     | ns   |

| t <sub>d(o)</sub>   | output delay time                   | pins PSTART, PSTART_N                                     | -                      | -   | 1 / f <sub>MCLK</sub> | ns   |

| t <sub>PHZ</sub>    | HIGH to OFF state propagation delay | pins OUT1, OUT2, OUT3,<br>OUT4, OUT5, OUT6, OUT7,<br>OUT8 | -                      | -   | 1 / f <sub>MCLK</sub> | ns   |

Figure 8. RESET\_N Timing

AX5689

# 7 Functional description

### 7.1 Overview

The AX5689 is a controller IC for digital audio reproduction consisting of 8 digital signal processing blocks and 8 analog-to-digital converters along with programmable, flexible signal routing.

The AX5689 contains 8 low-latency ADCs which are optimized for fast and therefore stable control loop operation. The typical latency from analog signal change to bitstream output change is 1 clock cycle. ADCs may also be selected for auxiliary functions such as analog inputs or power supply sensing. The outputs of the ADCs may be decimated and made available through the serial digital output interface.

The device accepts up to 16 PCM input channels through a serial audio interface and 8 balanced analog inputs through its ADCs. The serial audio interface can also deliver up to 8 channels of data from internal nodes or low-pass filtered and decimated ADC signals back to the host.

The AX5689 furthermore contains 8 sophisticated digital control loop structures, consisting of volume control, second order sections and rounding controls. Each of the channels is separately configurable and programmable. Channels may be split or cascaded to create more complex structures.

An interleaving stage is provided for combining channel outputs in a BTL or multi-phase PWM manner.

A versatile PWM controller converts the signal to 1-bit form with a wide selection of pulse frequencies and modulation methods. The CMOS level PWM outputs can be fed directly to a switching power stage that is followed by an output reconstruction filter. The filter compensation in the can correct for a wide range of external filter configurations.

The device is programmed via an SPI or I2C interface. The interface provides access to all features and is used to define the data path.

The combination of these blocks in one IC makes the AX5689 suitable as a digital amplifier with ADC feedback loop encompassing external components such as a power stage and output filter, as illustrated in Figure 9.

Figure 9. Digital amplifier with low-latency ADC feedback

An amplifier that uses the AX5689 can achieve high performance at low cost as all error sources within this loop are highly suppressed by the loop gain. This results in relaxed requirements for e.g. the power supply, the power stage and output filter components, thus making it easier to optimize the costs of the system.

## Digital Audio Converter and Amplifier Controller

## 7.2 Control interface

The control interface provides read and write access to the AX5689 control registers and consists out of four external I/O pins that may be operated in either SPI mode or I2C mode. In both modes, the AX5689 will act as slave device. Operation of this interface is asynchronous with respect to the audio sample rates.

The control interface is set to I2C mode. In I2C mode, pin CSN\_AD0 and pin MISO\_SDA set the desired AD0 and AD1 bit state of the I2C slave address. The control interface is put into SPI mode if a negative edge on pin CSN\_AD0 is detected. Ensure that the CSN\_AD0 and MISO\_SDA pin are set to a fixed value using a pull-up or pull-down resistor to prevent unintentional change over from I2C mode to SPI mode.

### 7.2.1 Protocol

The protocol definition applies to the data words of the communication cycles via the control interface and is independent of the chosen interface mode. The number of data words transferred is unlimited and fully determined by the master device controlling the control interface. Each data word consists of 16 data bits while the bit order of all data words is MSB first.

The data word composition is shown in Table 13. For write cycles, the first data word contains the autoincrement enable bit (AINC), 5 don't care bits and the 10-bit register address pointer (RAP). Any additional data words are treated as register write data (RWD), therefore writing the second data word to the register indicated by the register address pointer. When the auto-increment bit is set, the register pointer will be incremented by one after the data word has been written to allow successive RWD words being written to consecutive register addresses. Note that when the AINC bit is cleared, successive RWD words are being written to the same currently selected register.

| Word number | Bit number      |         |    |    |    |    |           |   |   |   |   |   |   |   |   |   |

|-------------|-----------------|---------|----|----|----|----|-----------|---|---|---|---|---|---|---|---|---|

| word number | 15              | 14      | 13 | 12 | 11 | 10 | 9         | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0           | AINC don't care |         |    |    |    |    | RAP (9:0) |   |   |   |   |   |   |   |   |   |

| 1           | RWD             | RWD     |    |    |    |    |           |   |   |   |   |   |   |   |   |   |

| 2           | RWD+            | RWD+1   |    |    |    |    |           |   |   |   |   |   |   |   |   |   |

|             |                 |         |    |    |    |    |           |   |   |   |   |   |   |   |   |   |

| n           | RWD+            | RWD+n-1 |    |    |    |    |           |   |   |   |   |   |   |   |   |   |

#### Table 13. Control interface data word composition

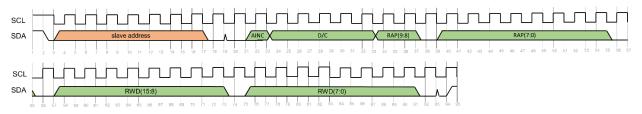

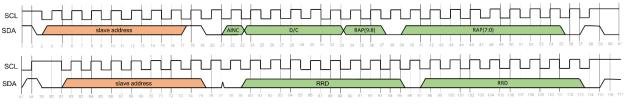

### 7.2.2 I<sup>2</sup>C Mode

This operation mode of the control interface requires two interface pins for the actual communication, SCL and SDA. The remaining interface pins AD0 and AD1 are used for I2C slave address configuration.

The SDA pin is a bidirectional data pin used to transfer data into and out of the control interface synchronous to the clock signal on the SCL input pin. All communication cycles begin with a start condition (negative edge on SDA while SCL is high) and are ended by a stop condition (positive edge on SDA while SCL is high). A repeated start condition may be generated instead of a stop condition, indicating the start of the next communication cycle. Data bits on SDA are valid when SCL is high and SDA transitions will only occur while SCL is low.

Each transferred data byte is being acknowledged by the receiver of the byte. Under normal conditions the acknowledge bit will be zero, indicating correct data transfer.

The first transferred byte consists of the MSB first 7-bit slave address and R /  $\overline{W}$  bit. The upper 5 bits of the I2C slave address are 01110. The two least significant bits are configurable by pins AD1 and AD0. Therefore, a maximum of four devices can operate in the same system in I2C mode.

| Fixed address |    |    |    |    | Pin conne | 7-bit<br>hexadecima |         |

|---------------|----|----|----|----|-----------|---------------------|---------|

| A7            | A6 | A5 | A4 | A3 | AD1       | AD0                 | address |

| 0             | 1  | 1  | 1  | 0  | 0         | 0                   | 38h     |

| 0             | 1  | 1  | 1  | 0  | 0         | 1                   | 39h     |

| 0             | 1  | 1  | 1  | 0  | 1         | 0                   | 3Ah     |

| 0             | 1  | 1  | 1  | 0  | 1         | 1                   | 3Bh     |

#### Table 14. I2C-bus slave address table

Figure 10. I<sup>2</sup>C write cycle

For read cycles, the I2C master shall indicate that it has received all data by making the last acknowledge bit one. Hereafter a stop condition or repeated start condition shall occur.

Figure 11. I<sup>2</sup>C read cycle

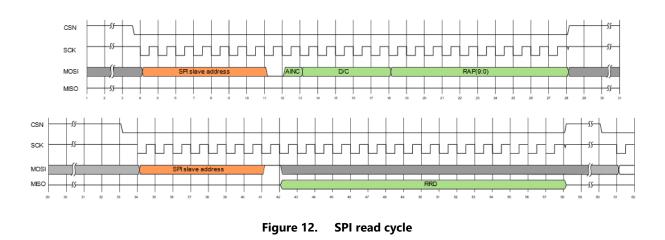

### 7.2.3 SPI Mode

In SPI mode, the chip uses the SCK, MISO, MOSI and CS\_N pins. Data written to the control interface is received via the MOSI pin, while data read from the control interface will be transferred via the MISO pin. Data transfers are synchronous to the clock signal on the SCK input pin. The default state of SCK is high (also known as CPOL=1) and communication cycles are enabled by a logic low level on CS\_N. The data bits are captured (MOSI) at the positive edge of the bit clock and are shifted out (MISO) at the negative edge of the bit clock (also known as CPHA=1). During data write cycles, the control interface keeps its data output in high impedance state.

## Digital Audio Converter and Amplifier Controller

The lower 2 bits of the SPI slave address are, unlike in I2C mode, not configurable and are fixed at "11". Therefore, the default SPI slave address is 0111011.

Figure 13. SPI write cycle

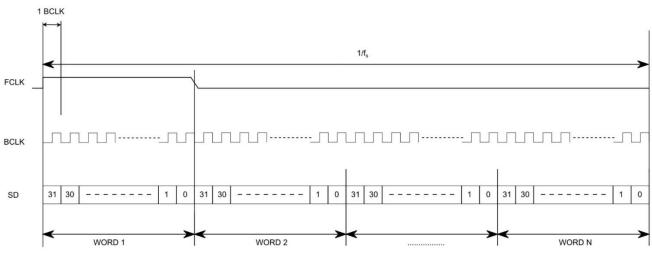

## 7.3 Serial audio Interface

The serial audio interface is used for in- and outputting data into and from the AX5689. The AX5689 is a slave on its serial audio input and a master on its serial data output. The register bits controlling audio format, word length and loop filter channel allocations are summarized in Table 18 for serial data transmitter and Table 19 for serial data receiver.

### 7.3.1 Audio formats

All formats can send MSB or LSB first and support frame lengths of 2, 4, 8 and 16 (receiver only) words, and word lengths of 16, 24 and 32 bits. Data may be sampled on the rising or falling edge of BCLK.

The number of BCLK clock cycles per FCLK clock cycle should be equal to the number of bits per word times the number of words per frame. A frame is synchronized to the active going flank of FCLK, or optionally one BCLK cycle after the active going flank of FCLK. There is no FCLK to BLCK word synchronization of the slots within a frame.

The data bits are all assumed to be significant. Given the requirement on BCLK with respect to FCLK there is no need for left or right justification. Should the data contain a different number of valid bits per word, zero padding is needed from the source. In case of invalid data, the last valid input data may be held.

The routing from the sub-frame data to the loop filters is programmable.

Digital Audio Converter and Amplifier Controller

Figure 14. Serial audio interface timing with default settings

Figure 15. Generalized TDM timing diagram

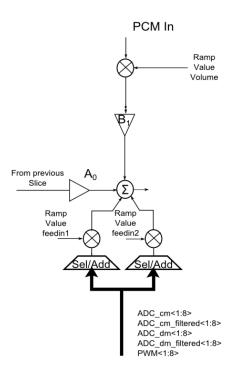

## 7.4 Feed-in filter

The inputs of the loop filters can mix signals coming from several parts inside and outside the AX5689. Each loop filter has four inputs:

- A PCM input which receives the mapped audio data times slots from the serial data receiver.

- Two feed-in inputs which can be connected to any ADC common or differential mode output, filtered versions thereof or any PWM outputs.

## Digital Audio Converter and Amplifier Controller

Output of the previous loop filter channel.

Figure 16. **Feed-in filter**

#### 7.4.1 Volume/ramp generators

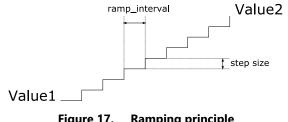

The inputs coming from the PCM, the feedin1 and feedin2 paths have ramp controls, these ramp controls can morph linearly between two end values called ramp value1 and ramp value2 as illustrated in Figure 17. The ramp transition time is governed by a step size value, a ramp interval time and ramp endpoint selection. The step size, ramp value1 and ramp value2 setting can be programmed for each channel, as shown in Table 26. The ramp interval is common for all channels. A separate ramp interval can be programmed for error mode, allowing for fast mute or switchover in error conditions. The ramp endpoint selection can be programmed for each channel. Table 17 shows the register description for the ramp endpoint and ramp interval setting.

Figure 17. **Ramping principle**

The maximum output of the loop filters is 0 dBFS. The system will hard-limit if the combination of coefficient settings and input signals results is larger than 0 dBFS.

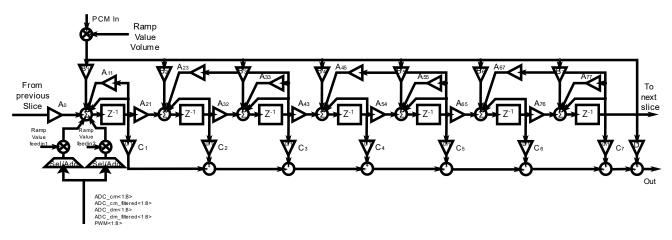

### 7.5 Loop filter

The loop filters are designed to be extremely flexible and versatile down to the configuration of the data path. This section describes the signal processing inside the control loop as shown in Figure 18. The input for the digital loop-filter is the digital input signal from the ramp and previous loop filter summation stage. The digital loop-filter consists of a programmable 7<sup>th</sup> order filter. The filter can be configured as a high-order noise shaping filter that makes sure noise and non-linearity generated inside the loop is suppressed. Each stage in the filter can be separately enabled by programming the *stage\_out\_enable* bit of each channel loop filter's control register, as shown in Table 27.

Figure 18. Loop filter slice including feed-in selection and volume/ramp generators

### 7.5.1 Zero detection

The states of all stages in the loop filter can be monitored for zero detection. Since LSBs can be quite noisy and thus upset the detection they can be masked off and only a certain number of MSBs used for the zero detection. This setting is possible by programming the *zerox\_setting* bit of each channel loop filter's control register, as shown in Table 27.

### 7.5.2 Limiting and clip detection

All stages inside the loop filter may be monitored for overflow by setting the *limit\_detect\_enable* bit of each channel loop filter's control register to zero or one, as shown in Table 27. When overflow occurs, it can either be ignored, detected or the value may be limited to the programmed threshold. The clip value can be programmed as an integer exponent, i.e. power of 2 below 0 dBFS.

### 7.6 Butterfly mixer

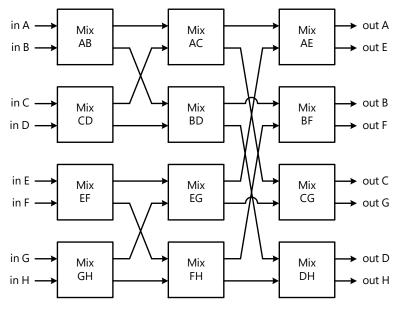

After the loop-filter a butterfly mixer mixes the signals from the various stages to enable MIMO processing.

Digital Audio Converter and Amplifier Controller

Figure 19. Butterfly mixer

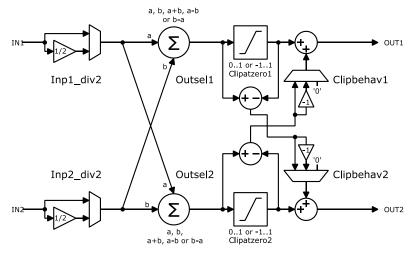

The butterfly mixer as shown in Figure 19 mixes the various loop filter outputs to enable a variety of MIMO filter operations, such as differential and common-mode control filters or more complex multipath versions. The structure of the mixer resembles that of a radix-2 FFT. Each butterfly element can mix two of its inputs in a variety of ways as shown in Figure 20.

Figure 20. Butterfly mixer element

Inputs to the data paths may be halved by programming the input div2 dividers. Subsequently the 'outsel' operators can either select or combine the two input paths.

# Digital Audio Converter and Amplifier Controller

The clip control mechanism inside the butterfly mixer elements can limit the maximum and minimum signal levels. The clip compensation functionality can also prevent common-mode clipping from becoming visible in the differential mode signal.

The signal range is either between -1 and 1 (clipatzero = 0) or between 0 and 1 (clipatzero = 1). Values outside the range are clipped. When an output path clips, clipbehav determines whether either each data path clips separately (0), the remainder from clipping is added in the other path (1) or the remainder from clipping is subtracted in the other data path (2).

## 7.7 Pulse Width Modulator (PWM)

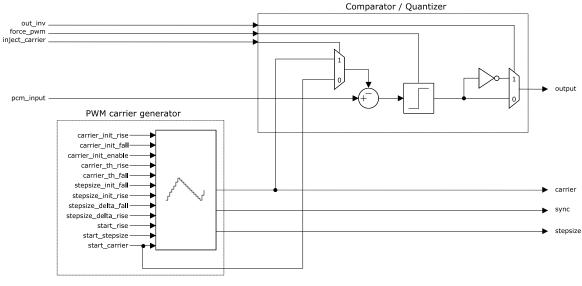

The pulse width modulator translates its PCM input signal into 1-bit output signals. There are two main elements to the PWM block, the carrier generator and the comparator / quantizer. The AX5689 has eight independent pulse width modulators. The block schematic is shown in Figure 21.

Figure 21. PWM block diagram

In normal operational mode, the PWM carrier block generates a triangle wave which is subtracted from the input signal, and the result is quantized to two levels, thus comprising the modulator function.

### 7.7.1 Carrier generator

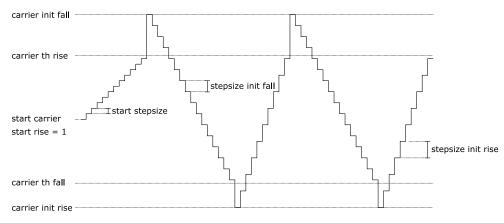

The carrier generator in the pulse width modulator can be programmed for frequency and shape. The general shape of the PWM carrier is shown in Figure 22.

Digital Audio Converter and Amplifier Controller

Figure 22. First order PWM carrier wave and variables governing its shape

The triangle wave is constructed as follows: the system starts at level *start\_carrier* and rises or falls, depending on *start\_rise*, with *start\_stepsize* until it reaches the level of *carrier\_th\_rise*. Upon reaching this threshold the waveform jumps to *carrier\_init\_fall* and starts to fall by *stepsize\_init\_fall* until it reaches the lower threshold *carrier\_th\_fall*. From there it jumps to *carrier\_init\_rise* and rises with *stepsize\_init\_rise* and the cycle repeats.

Any of the variables named above may be freely chosen. From the step size combined with the distance between *init* and *threshold* levels, the PWM triangle cycle time and therefore PWM carrier frequency may be calculated. It follows that different channels can have different frequencies, but also that channels may have a phase offset with respect to each other, determined by the initial values of the carrier.

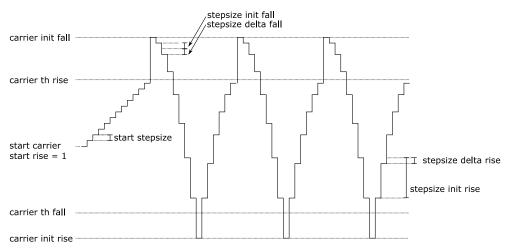

It is furthermore possible to make a second order PWM waveform by using the *stepsize\_delta* parameters, such that every step has a different size.

Figure 23. Second order PWM carrier wave and variables governing its shape

In Figure 23 again a waveform is constructed using the variables used in Figure 22, but this time the rising slope has a negative *stepsize\_delta\_rise*, causing the steps to become ever smaller, and the falling slope has a positive

## Digital Audio Converter and Amplifier Controller

*stepsize\_delta\_fall*, causing the steps to become ever larger. Thus, a non-linear second order PWM carrier is constructed. Care must be taken with negative delta values such that the step size does not become zero before the corresponding carrier threshold is reached.

### 7.7.2 Comparator/quantizer

The comparator block performs the modulation of the signal with the carrier and subsequently truncates the output to 1 bit.

To support both PDM and PWM outputs, control bits have been added. The *force\_pwm* bit allows the quantizer to only emit one falling edge during the rising flank of the PWM carrier and one rising edge during the falling flank of the PWM carrier, even if the signal moves erratically around the carrier signal. Setting this bit thus ensures a fixed PWM frequency.

On the other hand, the *carrier\_inject* bit, when set to zero, subtracts no carrier wave form in the comparator, reducing it to a 1-bit quantizer and thus turning the system into a PDM system. Instead of the carrier triangle wave, a fixed level of *start\_carrier* is subtracted. When this is not desired, *start\_carrier* should be set to zero. Optionally, the output may be inverted by setting *out\_inv* to 1.

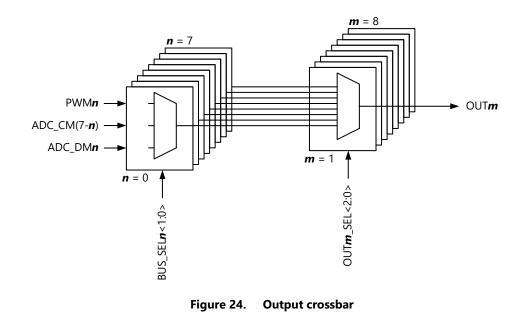

### 7.8 Output crossbar

In the crossbar, different routing options are possible. The crossbar is a multiple-input multiple-output (MIMO) block that supports flexible routing options, where every output could be programmed to pass along PWM outputs or either of the differential-mode or common-mode ADC outputs. The structure of the crossbar is shown in Figure 24.

The routing possibilities can be exploited by configuring the configuration registers that control the select lines of each multiplexer. Refer to Table 22 for the outputs crossbar configuration register description.

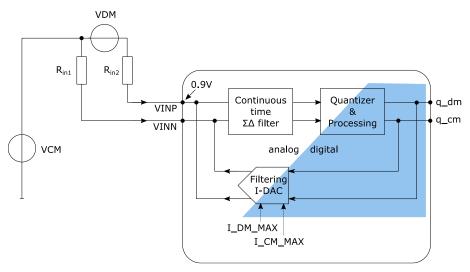

## 7.9 Low-latency ADC (LLADC)

The eight low latency ADCs on the AX5689 are of a special type of continuous-time sigma-delta ADC. Its low latency is made possible by bit stream outputs (q\_dm and q\_cm) which are fed back into an internal DAC with a tracking behavior as illustrated in Figure 25. Its outputs therefore track the input signal inside the signal bandwidth. The resulting system is robust towards jitter and other error sources typically associated with continuous-time 1-bit converters.

Figure 25. Low-Latency ADC principle diagram

The low latency ADC is a true differential current input ADC. It converts both single-ended and differential currents into separate bitstream outputs. By merit of a current input it can convert signals with amplitudes and biasing levels well outside its own supply level.

The ADC input terminals IN**x**P and IN**x**N (**x** = 1 to 8) are virtual grounds which sense current and are biased at a reference voltage of 0.52 V after initialization. This voltage is derived from an integrated bandgap referenced circuit. The voltage on the outside terminals of  $R_{in1}$  and  $R_{in2}$  are thus converted into input currents.

The ADC feedback loop tracks these input currents in the DAC by recreating the common mode currents and the differential mode currents such that the currents going into the  $\Sigma\Delta$  filter tend to zero. In doing so it has digitized the input currents and hence input voltages into bitstreams q\_dm and q\_cm.

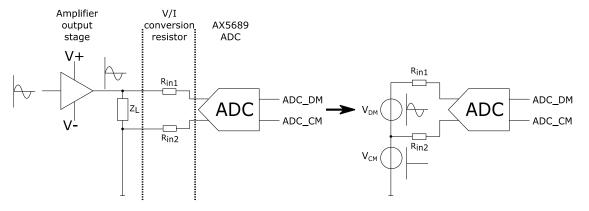

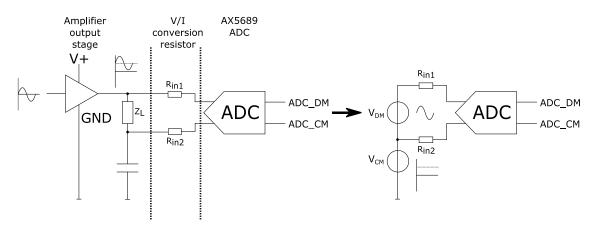

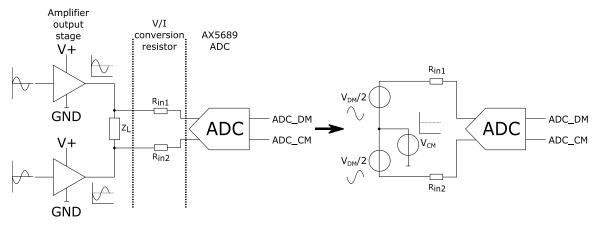

An overview of possible use cases that the ADC can handle is given in Figure 26, Figure 27 and Figure 28.

# Digital Audio Converter and Amplifier Controller

Figure 26. DC coupled Single Ended ADC use case.  $V_{DM} = V(Z_L)$ ;  $V_{CM} = V_+ + V_- = 0$

Figure 27. AC coupled Single Ended ADC use case.  $V_{DM} = V(Z_L)$ ;  $V_{CM} = V_+/2$

# Digital Audio Converter and Amplifier Controller

By selecting the correct value of voltage-to-current conversion resistors  $R_{in1}$  and  $R_{in2}$  an application can be scaled to arbitrary voltage levels. To minimize differential-mode to common-mode conversion and vice versa, the matching between  $R_{in1}$  and  $R_{in2}$  is critical, but only on a channel by channel basis.

### 7.9.1 Full-scale differential mode current scaling

For maximum system performance it is advised to use the full range of the LLADC. However, to save power, the current that leads to full-scale bitstream output (q\_dm) may be scaled down. The differential full-scale current scaling affects all ADC channels simultaneously.

The full-scale differential mode input current is given as

The default value for *REFGEN\_IREF\_FIR\_VALUE* is 47 which leads to a maximum input differential current of 7.5 mA.

The AX5689 ADCs have a modulation depth of 64%, which means that the signal swing based on I\_MAX\_DM should be scaled to this:

$$I_SIG_DM = I_MAX_DM * 0.64$$

Which for the default values leads to a maximum signal current of 4.8 mA.

In case an input differential voltage of 50V is to be digitized, this means that the external resistors  $R_{in1}$  and  $R_{in2}$  should be scaled to (50V - 0.6V) / 4.8mA = 10.3 k $\Omega$ .

### 7.9.2 Full-scale common mode current scaling

The maximum common-mode current that leads to full-scale common-mode bitstream (q\_cm) output is programmable as a fraction of the full-scale differential mode current. Contrary to the full-scale differential mode current scaling, the full-scale common-mode current scaling is programmed on a channel by channel basis.

In general, it is advised to scale the full-scale common-mode close to the expected average level rather than the worst-case occasional level for maximum stability.

The choice of common-mode current is highly dependent on the application. In case of a BTL application such as depicted in Figure 28 the voltages will always be positive; therefore, the sum of differential and common mode should always be positive, and hence the common mode should be equal to the differential mode.

In case of a single ended use case as depicted in Figure 26, the signal is symmetrical around zero and hence the common mode should equal half of the differential mode, such that the sum is symmetrical around zero.

The full-scale common-mode input current is given as:

I\_MAX\_CM = I\_MAX\_DM \* FIR\_CUR\_RATIO / 21

The default value for *FIR\_CUR\_RATIO* is 26 which leads to roughly a ratio of 1:1 between differential and common-mode current ranges.

# Digital Audio Converter and Amplifier Controller

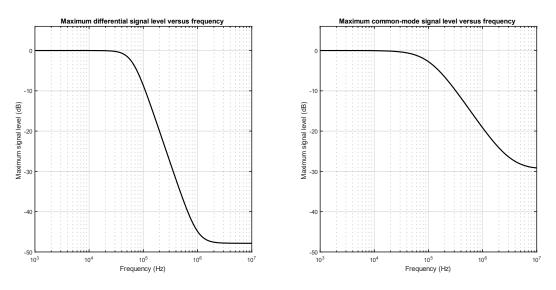

### 7.9.3 Input scaling versus frequency

The low latency ADC behaves like a tracking ADC with noise-shaping. As with other tracking ADCs the low latency ADC has a frequency-dependent maximum signal that it can convert. The maximum signal levels are given in Figure 29 (separated for differential and common-mode signals and normalized to 0 dB at low frequencies).

Figure 29 - ADC maximum signal levels

It is important that the input signals to the ADC do not exceed these maximum signal levels in order not to overload the ADC. It is hence important that at least some reconstruction filtering is used between the switching output and the ADC feedback.

### 7.10 Power stage control

The AX5689 has four pins which can be used to interact with a power stage. Pin PSTART and PSTART\_N are used to enable/disable the power stage. Pin PFAULT\_N and PWARN\_N handle fault and warning signals from the power stage.

#### 7.10.1 PSTART and PSTART\_N

Outputs PSTART and PSTART\_N operate exactly the same except for their opposite active-HIGH and active-LOW state. Both outputs are in High-Z state during a supply power-up sequence and as long as the RESET\_N input is active.

#### 7.10.2 PFAULT\_N

The active-LOW PFAULT\_N input is used to handle the power stage fault conditions like: overvoltage, undervoltage, short-circuit protection and over temperature protection. When pin PFAULT\_N is active the AX5689 controls the PSTART and PSTART\_N signals to disable the power stage. Once the power stage fault is resolved the AX5689 controls the PSTART and PSTART and PSTART\_N signals to enable the power stage again.

# Digital Audio Converter and Amplifier Controller

### 7.10.3 PWARN\_N

The AX5689 has a PWARN\_N input, which is active low. When this input is low, the PCM volume starts to ramp down. When the input becomes high, the PCM volume starts to ramp up. The slope of the volume ramp can be set by *pcmvol\_ramp\_interval* (see Table 17). The volume ramp transition time (from max volume to zero volume) can be calculated as follows:

$t_{ramp} = \frac{ramp\_value2 - ramp\_value1}{stepsize \cdot f_{mclk}} \cdot 16 \cdot (pcmvol\_ramp\_interval + 1)$

Where  $t_{ramp}$  is the ramp transition time,  $f_{mclk}$  is the master clock frequency of the AX5689, and *pcmvol\_ramp\_interval* is the value of register 0007h. The number of steps is set using the volume ramp register settings. For channel A, the volume ramp registers are *ramp\_value1* (register 0040h), *ramp\_value2* (register 0041h) and *stepsize* (register 0042h). See the <u>register map</u> for the volume ramp register base addresses of channel B to H.

### 7.11 Mode control

### 7.11.1 RESET\_N pin

The AX5689 has an active low RESET\_N pin. Activating the reset will set all hardware registers to their default value. After releasing the reset the device must be initialized again.

### 7.11.2 STATUS pin

The AX5689 can diagnose several internal and external conditions. The status of the diagnosis is stored in three registers. The registers have a dual function where a read command will output the information of the register, and a write to the same register will influence its mask setting. The following conditions can be detected for all channels:

- Channel loop filter output polarity.

- Loop filter zero; zero is detected when the number of MSB bits used for zero detection as configured in the loop filter settings are zero.

- Positive or negative clipping; separate for each channel but combined over all channel states.

In addition, the following global conditions are indicated:

- PWARN\_N pin status

- Mute status

- Serial data receiver status

- PFAULT\_N pin status.

The complete set of status registers is listed in Table 24.

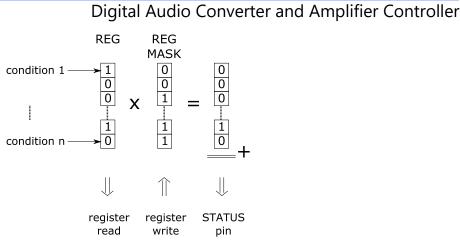

The STATUS pin is activated if the logical OR of any of the bitwise AND operations between the status bits and mask conditions equals one, see Figure 30.

Figure 30. Overview of status register and STATUS pin

If all the mask bits are set to zero, a register read of any of the status bits will return its momentary state which will not persist in the register when the condition itself disappears. If mask bits are set to one, then the corresponding condition will activate the STATUS pin.

Upon activation of the STATUS pin the pin state and the set of register conditions that triggered it are frozen until the three status registers have been cleared. To clear the status registers, read the three registers (address 003Ch to 003Eh) in consecutive order. If a single status register is read the status information is not cleared. Registers which have their mask bit set to zero are not cleared after read.

#### 7.11.3 MUTE\_N

Activating the mute pin will ramp to Value1 for each loop filter. Setting Value1 to zero will then perform a full soft mute.

Volume ramp setting

Soft mute: From 0 dB to full mute

Figure 31. Volume control behavior in waveforms

### Digital Audio Converter and Amplifier Controller

### 7.12 Startup and shutdown

The following flow gives an high-level description of device initialization after reset and its channel startup/shutdown procedure for a typical application. Depending on the application needs, alternative flows may be better suited. Please, refer to Axign's reference designs for a detailed implementation of the startup and shutdown procedure.

### 7.12.1 Initialize

The following steps list the sequence to initialize the device:

- 1. Power-up the AX5689. Recommended order for supply power-up is VDD(IO) first, followed by VDDA and VDDD. Keep the RESET\_N input logic-LOW during supply power-up to prevent unknown output conditions.

- 2. Power-up the supplies of the power stage (proper connections to the PSTART/PSTART\_N pins ensures that it remains inactive).

- 3. Apply a 49.152 MHz clock to the MCLK input.

- 4. Provide digital I2S/TDM stream to the serial audio port.

- 5. Set RESET\_N pin to logic-HIGH.

- 6. Configure data path connections, mute, signal processing coefficients and other settings via the I2C/SPI control port.

- 7. Enable the bandgap reference and reference ADC. Wait for the reference ADC to settle.

### 7.12.2 Startup

Startup the audio channels using the following sequence of steps:

- 1. Enable the loop filters and PWM modulators.

- 2. Enable external ADC feedback.

- 3. Enable the power stage.

- 4. Unmute the audio path by setting MUTE\_N pin to logic-HIGH. Wait for mute sequence to complete.

### 7.12.3 Shutdown

To shut down the device use the following sequence of steps:

- 1. Mute the audio path by setting MUTE\_N pin to logic-LOW. Wait for mute sequence to be completed.

- 2. Put the power stage in high-Z. Wait for the power stage to shutdown.

- 3. Disable external ADC feedback.

- 4. Disable the loop filters and PWM modulators.

### Digital Audio Converter and Amplifier Controller

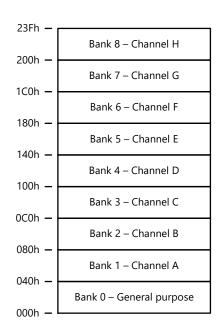

### 8 Register map

The memory map consists out of 576 × 16-bit words. The registers are divided into 9 banks of 64 registers each. General configuration data is stored in bank 0 and channel specific configuration data in bank 1 to 8. The total memory size is 9.216 kbit. Figure 32 shows the register map with the 9 banks and their base addresses. The detailed register bit descriptions show the offset address with respect to the base address of the bank.

memory address = base address + offset address

Figure 32. Register map

### 8.1 Bank 0 – Programming mode registers

| Offset<br>address | Register    | Bit                  | Symbol               | Access | Value                                                                    | Description                                                              |

|-------------------|-------------|----------------------|----------------------|--------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|