# Active PWM Ripple Reduction in Class-D Amplifiers using Digital Loop Filters

Christiaan E. Lokin

## ACTIVE PWM RIPPLE REDUCTION IN CLASS-D AMPLIFIERS USING DIGITAL LOOP FILTERS

### ACTIVE PWM RIPPLE REDUCTION IN CLASS-D AMPLIFIERS USING DIGITAL LOOP FILTERS

### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. ir. A. Veldkamp, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 24 maart 2023 om 16.45 uur

door

Christiaan Egidius Lokin

geboren op 19 januari 1992 in Hengelo, Nederland Dit proefschrift is goedgekeurd door:

Promotor prof. dr. ir. B. Nauta

Co-promotor dr. ir. R.A.R. van der Zee

This research is part of the Intelligent Class-D Control project (no. 13911) and is supported by the Applied and Engineering Science division (TTW), which is part of the Netherlands Organization for Scientific Research (NWO).

UNIVERSITY University of Twente P.O. Box 217, 7500 AE Enschede, Netherlands

Cover Design: Jesse Haaksman

Printed by: Gildeprint Drukkerijen, Enschede, The Netherlands

Lay-out: Chris Lokin, typeset with LATEX

978-90-365-5566-1 ISBN (print): ISBN (digital): 978-90-365-5567-8

URL: https://dx.doi.org/10.3990/1.9789036555678

Copyright © 2023 by Christiaan Egidius Lokin, Enschede, The Netherlands.

All rights reserved. No parts of this thesis may be reproduced, stored in a retrieval system or transmitted in any form or by any means without permission of the author. Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd, in enige vorm of op enige wijze, zonder voorafgaande schriftelijke toestemming van de auteur.

### Samenstelling promotiecommissie:

Voorzitter en secretaris:

prof. dr. J.N. Kok Universiteit Twente

Promotor:

prof. dr. ir. B. Nauta Universiteit Twente

Co-promotor:

dr. ir. R.A.R. van der Zee Universiteit Twente

Leden:

prof. dr. T. Batista Soeiro Universiteit Twente dr. ir. A.B.J. Kokkeler Universiteit Twente

prof. dr. K.A.A. Makinwa TU Delft prof. dr. ir. L.J. Breems TU Delft Opgedragen aan mijn ouders

"Do, or do not. There is no try."

– Grandmaster Yoda

### **ABSTRACT**

The research field around sound reproduction is driven by a desire to continuously pack more powerful amplifiers in a small fan-less enclosure while providing state-of-the-art noise and distortion performance. Class-D amplifiers are a perfect candidate for these requirements, specifically because of the inherently low dissipation in their switching power stage with respect to more conventional linear amplifiers. There is, however, always a caveat: switching high currents at high frequencies causes electromagnetic emissions that could interfere with the correct operation of other electronic devices. Regulations limit the amount of electromagnetic interference (EMI) that devices are allowed to emit to maintain interoperability between the many electronic devices in the Internet of things (IoT) era.

Speakers are commonly connected to an amplifier using leads of several meters. These leads double as an antenna for high frequency signals above the audio band, such as the switching frequency and its harmonics or parasitic ringing in the output stage, thereby causing unwanted radiated emissions. This thesis is focused on reducing the EMI due to the residual power after the output filter at the pulse-width modulation (PWM) frequency, the so called ripple. Examples in literature reduce the power at the PWM frequency and its harmonics by applying spread spectrum modulation to smear power out over a larger bandwidth. However, in this way they still radiate the same amount of power, just not concentrated at distinct frequencies. To reduce the ripple current through the speaker leads, it is possible to use a higher order filter, use a multi-phase or multi-level output stage or to inject a cancellation signal after the output filter. In the research field of power electronics, cancellation schemes have been presented. First the disturbance is sensed and processed and afterwards a cancellation signal is synthesized and injected into the circuit. The processing can be done using a feedback or feed-forward topology, each having its advantages and disadvantages.

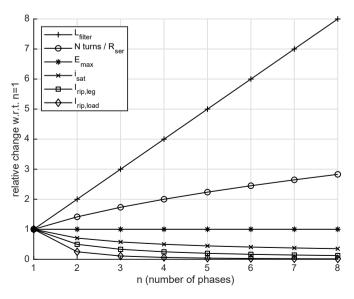

An extensive case study on multi-phase systems is done to evaluate their merits in reducing the ripple current after the output filter. In a multi-phase system, multiple half-bridges are combined in a parallel fashion to drive one or both sides of the load. Interleaving of the PWM carriers in the modulator corresponding to each half-bridge provides a reduction in the observed ripple current after combining the half bridge outputs in the output filter. The effect of adding more phases on the amount of ripple is

studied as well as the costs associated to multi-phase implementations.

In the field of power conversion, multi-level systems are often used to relax the output ripple by switching between multiple voltage levels. By reducing the voltage steps, the emissions are also lowered which is especially of importance when switching powers in excess of 1 kW. Different multi-level architectures are discussed to find whether they are applicable in audio amplifiers or not.

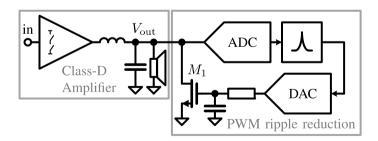

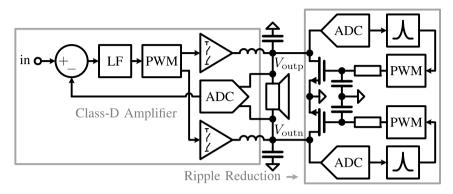

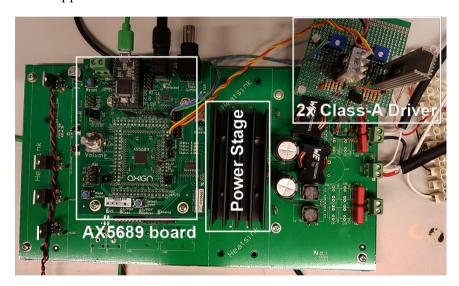

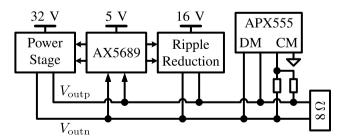

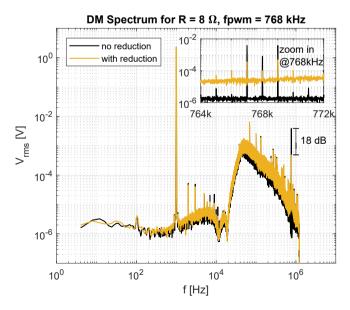

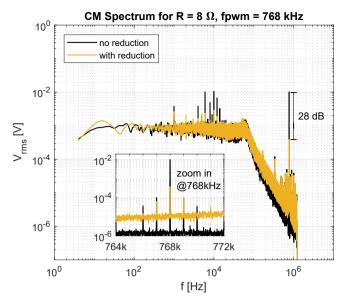

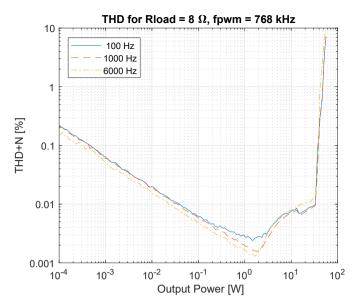

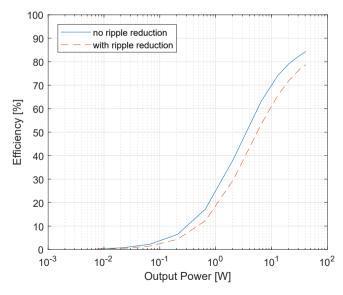

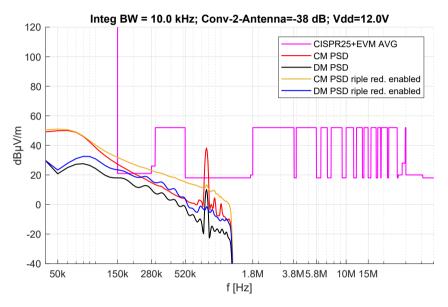

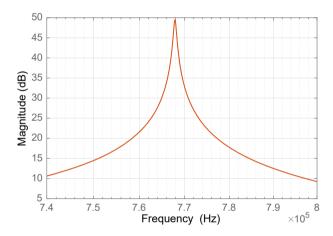

The feasibility of the aforementioned techniques has been considered with the main goal of having a system with fewer external components. Multi-phase and multi-level systems are hence not a suitable choice and a further case study between feed-forward and feedback ripple reduction techniques showed the latter to be the most straightforward to implement. A development board made by Axign utilizing the AX5689 digital amplifier controller IC was used as a design vehicle to realize a prototype bridge-tied-load (BTL) Class-D amplifier with ripple reduction. The builtin analog-to-digital converters (ADCs) were used to measure the output signals of both bridge halves. A selective digital band-pass loop filter was designed in the digital signal processor (DSP) core of the AX5689 to only provide high loop-gain around the PWM frequency without affecting the audio band. A ripple reduction of 28 dB for the common-mode (CM) and 18 dB for the differential mode (DM) was achieved across all signal frequencies and output powers up to 10 W. The Class-A drivers used to inject the anti-ripple have a negative impact on the total system efficiency, which drops from 84% without ripple reduction to 79% with ripple reduction enabled. The technique has virtually no impact on total harmonic distortion plus noise (THD+N) performance and could be used as an add-on to any Class-D amplifier with a fixed PWM frequency. Efficiency still has to be improved to make the solution more attractive for the industry. A monolithic realization of the system could further improve the efficiency and the ability to reduce the ripple.

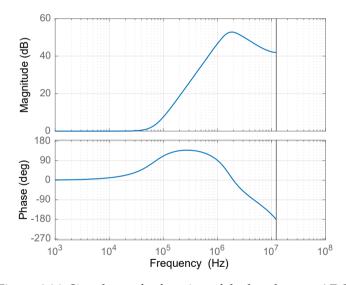

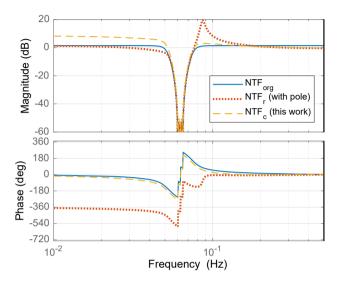

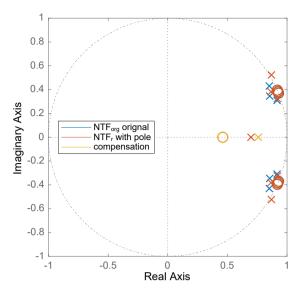

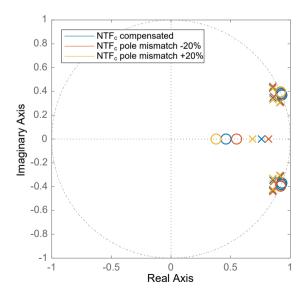

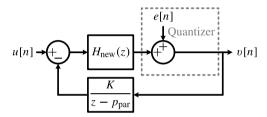

Designing the digital band-pass filter of the prototype faced some challenges regarding processing delay. Compensating dynamics near the sample frequency becomes more difficult when processing delay is present. Ways to mitigate the effect of non-fractional delays on loop stability have been investigated and compared to similar techniques. In the research field of continuous-time  $\Sigma\Delta$  ADCs, a technique called excess loop delay (ELD) compensation is used to stabilize the loop filter in presence of a known delay in the feedback path. When the quantizer delay is less than one clock cycle, it is possible to restore the noise transfer function (NTF) to that of the delay-less system by tuning the loop-filter coefficients and adding a direct path around the quantizer. Quantizer delays in excess of one clock cycle do not allow for full restoration of the desired NTF. This phenomenon shares similarities to our proposed delay mitigation technique. The impact of both techniques on noise-shaping performance are analyzed and the proposed method is shown to also have merits in mitigating the effect of parasitic

high-frequency poles.

In summary, this thesis has shown a technique to reduce the ripple current after the output filter. Thereby the amount of EMI that can be radiated off the speaker leads decreases. The effect of unit delays in the loop has been mitigated by applying a special filter design method to obtain a more stable system. A prototype has been made around an existing amplifier to show the effectiveness of the proposed feedback ripple reduction solution.

### **SAMENVATTING**

Een belangrijk thema in het onderzoeksveld rond geluidsreproductie is de vraag naar krachtige versterkers in een kleine behuizing zonder ventilator terwijl ze hoogwaardige ruis- en vervormingsprestaties leveren. Klasse-D versterkers zijn een perfecte kandidaat om te voldoen aan deze eisen, met name vanwege de lagere dissipatie in hun schakelende vermogenstrap in vergelijking tot conventionele lineaire versterkers. Er zit echter een addertje onder het gras: het schakelen van hoge stromen op hoge frequenties veroorzaakt elektromagnetische interferentie (EMI) die de werking van andere elektronica kunnen verstoren. Er is regelgeving waarin is vastgesteld hoeveel elektromagnetische interferentie apparaten mogen uitzenden om samen te kunnen blijven werken met het toenemend aantal elektronische apparaten in onze wereld.

Luidsprekers worden gewoonlijk met kabels van enkele meters aangesloten aan een versterker. Deze draden werken ook als antenne voor hoogfrequente signalen boven de audio band, zoals de schakelfrequentie en de hogere harmonischen ervan of parasitaire oscillaties in de uitgangstrap, waardoor er ongewenste emissies plaatsvinden. Dit proefschrift richt zich op het verminderen van EMI veroorzaakt door het schakelresidu van de pulsbreedte modulatie (PWM) na het uitgangsfilter, de zogenoemde rimpel. In de literatuur zijn allerhande voorbeelden te vinden om het vermogen op de PWM schakelfrequentie en de harmonischen ervan te verminderen. Bijvoorbeeld, door het toepassen van 'spread spectrum' modulatie, een techniek om het vermogen uit te smeren over een grotere bandbreedte. Desalniettemin wordt er op deze manier dezelfde hoeveelheid vermogen uitgezonden, alleen is het niet geconcentreerd op specifieke frequenties. Om de rimpelstroom door de luidsprekerdraden te verminderen, kan een hogere orde filter of een multifase of multilevel uitgangstrap gebruikt worden. Een andere optie is om een signaal in tegenfase te injecteren en zo de rimpel op te heffen na het uitgangsfilter. In het onderzoeksveld van vermogenselektronica zijn zulke opheffingsmethoden al bekend. Eerst wordt de verstoring gemeten en bewerkt, waarna een opheffingssignaal gesynthetiseerd kan worden voor injectie in het circuit. De signaalbewerking kan worden gedaan door middel van terugkoppeling of feed-forward topologieën met ieder zijn voor- en nadelen.

Er is een uitvoerige case study op het gebied van multifase systemen uitgevoerd om de mogelijkheden tot het reduceren van de rimpel na het

uitgangsfilter te evalueren. In een multifase systeem worden meerdere halfbruggen op een parallelle manier gecombineerd om één of beide kanten van de belasting aan te sturen. Door de PWM draaggolven op verschillende fasen te laten lopen, kan na het combineren van de uitgangen van de halfbruggen de rimpelstroom worden gereduceerd. Het gebruik van meer fases op de hoeveelheid rimpel is bestudeerd net als de bijbehorende kosten van multifase implementaties.

In het veld van vermogensomzetting worden vaak multilevel systemen die schakelen tussen meerdere spanningen gebruikt om de rimpel aan de uitgang te verminderen. Door het verkleinen van de spanningsstappen worden de emissies ook lager wat vooral van belang is wanneer vermogens hoger dan 1 kW worden geschakeld. Verschillende multilevel architecturen zijn bestudeerd om te kijken of ze toegepast kunnen worden in audioversterkers.

De haalbaarheid van de eerdergenoemde technieken is onder de loep genomen met als hoofddoel het vinden van een systeem met zo min mogelijk externe componenten. Multifase en multilevel systemen zijn daarom niet een geschikte keuze en een daaropvolgend onderzoek naar op feedforward en terugkoppeling gebaseerde rimpelreductietechnieken wees uit dat de laatstgenoemde techniek goed te implementeren is. Een prototype Klasse-D brugversterker met rimpelreductie is gerealiseerd op een bord van Axign met daarop de AX5689 digitale versterker aansturingschip. De ingebouwde analoog-digitaal omzetters (ADCs) zijn gebruikt om de uitgang van beide halfbruggen te meten. Een selectief banddoorlaat lusfilter is ontworpen in de digitale signaal processor (DSP) van de AX5689 met als doel om alleen veel versterking te maken op de PWM frequentie zonder de inhoud van de audioband aan te tasten. Dit resulteert in een rimpelreductie van 28 dB voor common-mode (CM) en 18 dB voor differentiële-mode (DM) signalen over de gehele audioband met signalen tot 10 W. De Klasse-A versterkers van het anti-rimpel injectiecircuit hebben echter een negatief effect op de efficiëntie, die van 84% zonder naar 79% met rimpelreductie zakt. De techniek heeft praktisch geen invloed op de totale harmonische vervorming plus ruis (THD+N) prestaties en kan als toevoeging voor een willekeurige Klasse-D versterker met een vaste schakelfrequentie worden gebruikt. De efficiëntie van het systeem moet nog verbeterd worden om interessant te worden voor de industrie. Een monolithische realisatie van het systeem zou kunnen helpen om de efficiëntie en rimpelreductie verder te verbeteren.

Het ontwerp van digitale banddoorlaatfilters van het prototype bevatte een aantal uitdagingen omtrent het omgaan met signaalvertraging. Het compenseren van dynamica in de buurt van de bemonsteringsfrequentie wordt lastiger wanneer er vertraging in het signaalpad zit. Manieren om de effecten van niet-fractionele vertragingen op de stabiliteit van de lus te verminderen, zijn onderzocht en vergeleken met vergelijkbare technieken. In het onderzoeksgebied van continue-tijd Sigma-Delta analoog-digitaal-

omzetters ( $\Sigma\Delta$  ADCs) wordt een techniek genaamd ELD compensatie gebruikt om de lus te stabiliseren wanneer een bekende signaalvertraging in het feedbackpad optreedt. Wanneer de quantizer vertraging minder dan één klokcyclus betreft, kan de ruisoverdracht (NTF) van het systeem zonder vertraging worden hersteld door middel van het aanpassen van de lusfiltercoëfficiënten en het toevoegen van een direct pad rondom de quantizer. Quantizer vertragingen langer dan één klokcyclus maken het onmogelijk om de ruisoverdracht volledig te herstellen. Dit fenomeen komt overeen met hoe onze techniek omgaat met vertragingen. De invloed van beide technieken op 'noise-shaping' prestaties is geanalyseerd en de voorgestelde methode laat ook zien dat er omgegaan kan worden met hoogfrequente polen.

Samengevat laat dit proefschrift een techniek zien die de rimpelstroom vermindert na het uitgangsfilter. Hierdoor wordt de hoeveelheid EMI die uitgestraald wordt van de luidsprekerdraden verlaagd. Het effect van klokcycli signaalvertraging in de lus is verholpen door het toepassen van een speciale filterontwerpmethode wat resulteert in een stabieler systeem. Een prototype is gerealiseerd rondom een bestaande versterker om aan te tonen dat de voorgestelde op terugkoppeling gebaseerde rimpelreductietechniek een effectieve oplossing is.

### LIST OF ACRONYMS

**AC** alternating current

**AM** amplitude modulation

**ADC** analog-to-digital converter

BTL bridge-tied-load

CM common-mode

CMOS complementary metal-oxide-semiconductor

**CRFF** cascade of resonators with feed-forward summation

**DAC** digital-to-analog converter

DC direct current

**DM** differential mode

**DMOS** double-diffused MOS

**DR** dynamic range

**DSD** Direct-Stream Digital

**DSP** digital signal processor

**ELD** excess loop delay

**EMI** electromagnetic interference

**FIR** finite impulse response

FIRDAC finite impulse response DAC

**FM** frequency modulation

**FPGA** field programmable gate array

HB half-bridge

IC integrated circuit

IIR infinite impulse response

IoT Internet of thingsLLADC low-latency ADC

LMS least mean squares

LSB least significant bit

LTI linear time-invariant

MAE minimum aliasing error

MOS metal-oxide-semiconductor

MOSFET metal-oxide-semiconductor field-effect transistor

NMOS P-type metal-oxide-semiconductor

**NSPWM** natural sampling PWM

**NTF** noise transfer function

**PA** power amplifier

PCB printed circuit board

**PCM** pulse-code modulation

**PDM** pulse-density modulation

**PEDEC** pulse edge delay error correction

**PMOS** N-type metal-oxide-semiconductor

**PSRR** power supply rejection ratio

**PWM** pulse-width modulation

**RF** radio frequency

**SAR** successive approximation register

SE single-ended

**SQNR** signal-to-quantization noise ratio

STF signal transfer function

THD total harmonic distortion

THD+N total harmonic distortion plus noise

### **C**ONTENTS

| Abstract · vii                              |

|---------------------------------------------|

| Samenvatting · xi                           |

| List of Acronyms · xv                       |

| 1 Introduction · 1                          |

| 1.1 Class-D Amplifiers · 2                  |

| 1.2 Analog PWM Generation · 2               |

| 1.3 Digital PWM generation · 6              |

| 1.4 Output stage · 9                        |

| 1.5 Class-D Non-idealities · 14             |

| 1.6 Research Questions · 17                 |

| 1.7 Thesis Overview · 17                    |

| 2 Overview of EMI Reduction Techniques · 19 |

| 2.1 Prior Art · 19                          |

| 2.2 Bridge-Tied Load · 19                   |

| 2.3 Switching Frequency Modulation · 23     |

| 2.4 Common-mode Modulation · 23             |

| 2.5 Multi-phase · 23                        |

| 2.6 Multi-level · 24                        |

| 2.7 Active Ripple Compensation · 30         |

| 2.8 Feed-forward Cancellation · 31          |

| 2.9 Research Questions · 31                 |

| 2.10 Conclusion · 31                        |

| 3 Multi-phase Class-D · 33                  |

| 3.1 1-phase Ripple Current · 34             |

| 3.2 Ripple in Two-phase systems · 35        |

| 3.3 Ripple in Multi-phase Systems · 37      |

| 3.4 Load Ripple · 38                        |

| 3.5 Output Filter · 41                      |

| 3.6 Multi-phase Trade-off 46                |

| 3.7 Conclusion · 50                         |

| 4 ACTIVE RIPPLE REDUCTION · 51              |

| χv | 111       |

|----|-----------|

|    | _         |

|    | ( )       |

|    | 0         |

|    | Ż         |

|    | $\exists$ |

|    | Ħ         |

|    | 7         |

|    | $\exists$ |

|    | ГŃ        |

| 4.1 Operation Principle · | 5 | ) |  |

|---------------------------|---|---|--|

|---------------------------|---|---|--|

4.2 Implementation · 58

4.3 Design Vehicle: AX5689 · 61

### 4.4 Ripple Reduction Loop Design · 65

4.5 Simulation results · 70

### 4.6 Experimental Results · 71

4.7 Discussion · 76

4.8 Conclusion · 77

### 5 FILTER DESIGN · 81

5.1 Introduction · 81

5.2 Prior Art · 83

5.3 Filter Design and Delay · 84

5.4 Mitigation Technique · 85

5.5 Results · 88

5.6 Conclusion · 99

5.A Mitigation of Multiple Poles ·100

### 6 CONCLUSIONS AND RECOMMENDATIONS ·103

6.1 Summary and Conclusion ·103

Discussion and Recommendations ·104 6.2

6.3 Original Contributions ·105

### References ·107

LIST OF PUBLICATIONS ·111

Peer-reviewed .111

Other ·111

ACKNOWLEDGEMENTS ·113

ABOUT THE AUTHOR ·117

CHAPTER 1

### Introduction

Society is making more and more use of electronic devices to fulfill work related tasks and to enjoy spare time. To provide means of interaction, transducers are used which convert for instance touch signals to the digital domain or an analog audio signal to sound pressure waves.

Class-D power amplifiers are well suited for audio amplification, and have hence become the standard for power amplifiers in electronics for consumer, mobile and automotive applications. High efficiency is realized by switching the power stage transistors on and off, eliminating the dissipation associated with Class-AB amplifiers. This allows for high power output in a small form factor, as only a modest heat sink suffices. Total harmonic distortion (THD) performance of Class-D amplifiers has become equal to, or better than, the performance of Class-AB amplifiers. Both the high efficiency and high audio performance have resulted in a growth in the use of Class-D audio amplifiers [1].

The increased efficiency of Class-D has side effects, namely electromagnetic interference (EMI) due to high frequency switching. It is common to use switching frequencies of several hundreds of kilohertz, which do produce harmonics in the AM radio band. Furthermore, the fast switching transients produce frequency content in the high megahertz range which can interfere with, for example, the FM radio band. As set-top box or car audio amplifier systems connect the speakers via long leads, these leads will function as an antenna for the common-mode (CM) switching residue.

In this chapter, the design space and common non-idealities of Class-D audio power amplifiers will be explored. First, both analog and digital pulse-width modulation (PWM) generation topologies will be discussed including ways to implement feedback. Subsequently, output stage topologies and their driver stages are discussed, including typical phenomena such as dead-time, hard-switching and soft-switching. Next, we will look

The 2<sup>nd</sup> and 3<sup>rd</sup> paragraph on this page have appeared in [CEL:3].

at the non-ideal effects in Class-D amplifiers, mainly focusing of EMI due to high-frequency switching voltages and currents. Also, the main dissipation mechanisms in Class-D amplifiers are shortly discussed. Finally, the chapter concludes with research questions and an overview of the remainder of this thesis.

### 1.1 Class-D Amplifiers

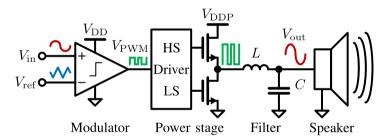

A Class-D amplifier can be subdivided into three blocks, a modulator, a power stage and a filter. An example of an analog Class-D amplifier is shown in Figure 1.1. The modulator converts the input signal into a PWM signal by comparing the input to a high-frequency triangular or sawtooth reference signal. The PWM signal is amplified by a power stage, which consists of level shifting circuits to drive the high- and low side power transistors from a higher supply voltage than the modulator. After the amplification, the high-frequency switching components are filtered out using an LC low-pass filter. A power stage also includes features to ensure robust operation, such as dead-time generation, over-current protection and click/pop reduction. To achieve good THD performance, a feedback loop is often implemented to counteract the non-linearity in the power stage.

Figure 1.1: Overview of an analog Class-D amplifier with idealized internal signals.

### 1.2 Analog PWM Generation

The first type of amplifier to be discussed is a Class-D amplifier that incorporates an analog signal processing path. A distinction between four PWM topologies can be made, namely fixed carrier systems with and without feedback and self-oscillating systems with either hysteresis or delay based feedback. These topologies are described in the following sections.

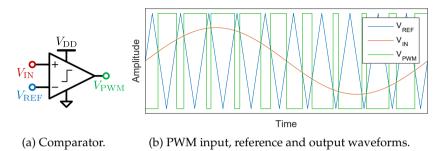

### 1.2.1 Fixed carrier

In a fixed carrier Class-D amplifier, the PWM signal switches at a constant frequency. The modulator consists of a comparator fed by a fixed frequency

saw-tooth or triangular reference and the input signal. The modulator output signal is high when the input signal is larger than the reference signal and the other way around. This method of modulation is called natural sampling PWM (NSPWM) and a comparator and its waveform signals are shown in Figure 1.2. Now, the PWM signal can be fed to an output stage to deliver power to the load.

Figure 1.2: NSPWM modulation.

A drawback of making an amplifier using this approach is that the system is feed-forward, hence there are no means of error suppression. Since the PWM signal is effectively multiplied with the supply rail, any variations on the supply voltage are directly present at the load, giving a power supply rejection ratio (PSRR) of 0 dB. Feed-forward power supply compensation has been proposed in [2] to mitigate the effect of power supply variations. Apart from disturbances in the the supply voltage, the output stage can not exactly reproduce the PWM waveform due to rise times and dead-time, which both cause distortion.

### **Feedback**

Because the feed-forward amplifier has a bad PSRR and distortion due to the output stage, this amplifier is usually equiped with a feedback loop to compensate for these errors. Different strategies have been proposed in literature, namely, voltage feedback either from the switching output node or post filter and output current feedback. The feedback loop should provide high loop gain in the audio band to provide sufficient error suppression. [3–7]

### 1.2.2 Self-oscillating

The other analog switched-mode amplifier is a self-oscillating amplifier, an amplifier that oscillates due to its feedback structure without requiring a reference signal. When the amplifier is idle its switching frequency is maximum. Increasing or decreasing the duty cycle by applying an input signal will reduce the switching frequency. Using near maximum modulation indices can impact the performance of the amplifier because

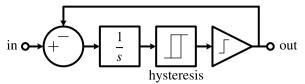

of low switching frequencies. Both a hysteretic and a delay based self-oscillating loop are shown in Fig. 1.3.

(a) Hysteretic self-oscillating topology.

(b) Delay based self-oscillating topology.

Figure 1.3: Self-oscillating feedback schemes.

### Hysteretic

In a hysteretic switched-mode amplifier the output signal is fed back and summed with the input signal at the input of an integrator. Then, the integrator output is fed to a comparator with a hysteresis window. This approach gives a second order loop transfer in the audio band using a single integrator [8]. A hysteretic feedback loop is shown in Fig. 1.3a.

### Delay based

A delay based switched-mode amplifier looks much like the hysteretic amplifier. However, instead of a hysteresis window, a time-delay is inserted after the integrator. The system provides a first order loop transfer but can be increased to a higher order by adding more integrator stages [9]. A delay based feedback loop is shown in Fig. 1.3a.

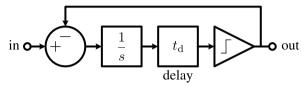

### 1.2.3 Distortion due to feedback

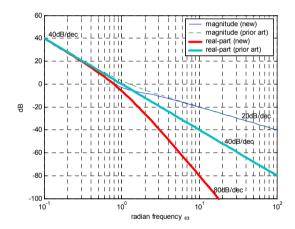

Applying feedback can cause non-linearities if not applied correctly. The ripple in a feedback system can interfere with the carrier in the PWM modulator, which can alias carrier side-bands into the audio band [4]. THD deteriorates especially when high-order loop filters are implemented. In order to circumvent this deterioration, minimum aliasing error (MAE) filters can be implemented. These filters utilize a low-pass feedback path from the output and a high-pass feedback path from before the PWM quantizer as shown in Figure 1.4. This structure can be reduced to a single linear time-invariant (LTI) filter which realizes a transfer function

Figure 1.4: PWM implementation with 2 feedback paths [3].

with a faster decaying real part at high frequencies when compared to a generic 2<sup>nd</sup> order loop filter as shown in Figure 1.5. The total system has improved THD because of the low DC error due to carrier aliasing, which is characteristic to a 1<sup>st</sup> order modulator, and a high loop gain corresponding to a 2<sup>nd</sup> order modulator [3].

Figure 1.5: Comparison between the traditional 2<sup>nd</sup>-order loop and [3].

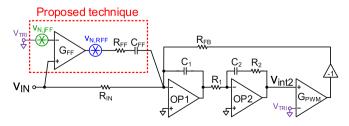

Another recent study has shown a feed-forward technique that injects a current to cancel the high-frequency PWM components in the feedback current before the first integrator (OP1 + C1) as shown in Figure 1.6. This

Figure 1.6: Model of the amplifier with the cancellation circuit[10].

6

approach improves the THD and has no influence on loop stability [10]. An improved design in [11] adds equalization to better match the phase of the cancellation current to the PWM components and linearizes the overall transfer of the amplifier.

By changing to a capacitive instead of a resistive feedback network and the application of choppers [12], it was shown that the performance limitations due to resistor noise in the feedback network can be mitigated reaching a dynamic range in excess of 120 dB.

### 1.3 Digital PWM generation

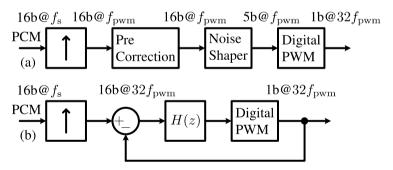

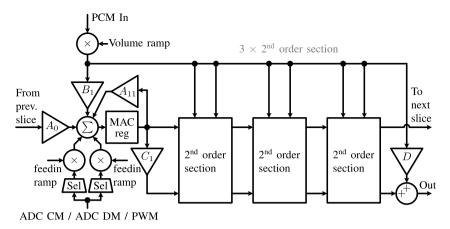

Another approach is to generate PWM signals in the digital domain. In order to do this the input signal should be presented as a bitstream, hence if the input signal is analog, it has to be converted to a digital bitstream. In case of a typical pulse-code modulation (PCM) input of 16-bit samples at a 48 kHz sample rate ( $f_s$ ), the input signal is up-sampled and noise-shaped afterwards to obtain a signal with fewer bits per sample, at a higher sample rate than the PCM signal. The PWM signal is obtained by comparing the up-sampled, noise-shaped signal to a digital staircase approximation of a triangular or sawtooth wave [13, 14], similar to operation of the analog PWM modulator previously discussed in this chapter. Two implementations are shown in Figure 1.7 containing the required sample-rates and bit-depths between the block [1].

Figure 1.7: Digital PWM (a) pre-correction (b) PWM- $\Sigma\Delta$  (adapted from [1]).

Another method is to noise-shape the input signal to a 1-bit signal, which effectively is pulse-density modulation (PDM) instead of PWM. Coincidentally, such a noise-shaped PDM signal is also the native way of storing the Direct-Stream Digital (DSD) bitstream audio format [15]. Just like a PWM signal, this PDM signal can be amplified and filtered to reconstruct the audio signal. However, amplifying a PDM signal requires a faster switching power stage due to the majority of the switching frequency content being around  $f_s/2$  compared to  $f_{\rm pwm}$  for PWM systems [16].

### 1.3.1 Open-loop

A conventional topology for digital class-D amplifiers is the feed-forward or open-loop topology. Like for analog class-D amplifiers there is no feedback mechanism, hence this type of amplifier requires a stable supply because the PSRR is low. Moreover, non-linearity introduced by the modulator and the output stage is also deteriorating the THD of the system. The output stage introduces pulse-width errors due to the inserted dead-time [13, 14, 17].

To compensate for the non-linearity of the modulator and the output stage, a pre-distortion can be applied to the input signal when the modulator and output stage distortion characteristics are known. A way to reduce modulator distortion was realized by implementing a Hammerstein filter [18]. Careful design of the output stage is required, tailoring the dead-time to keep distortion at a minimum without compromising reliability [19, 20].

### 1.3.2 Feedback

Many ways to apply feedback to digital class-D amplifier have been published in literature [5, 6, 13, 21–30]. Hybrid types of amplifiers that generated PWM digitally have been presented where the output stage has an analog loop to mitigate supply variations [5, 13]. An approach shown in [21] is called pulse edge delay error correction (PEDEC), an algorithm that changes the position of the switching edges to eliminate distortion in the power stage due to supply variations or non-linearity.

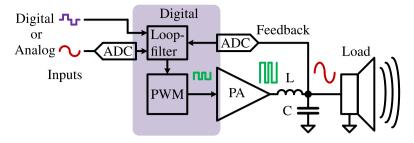

However, digitizing the feedback loop is a technique that is becoming possible due to the reduced feature sizes of the required digital logic. A low-power analog-to-digital converter (ADC) can be inserted into the feedback path to sample the output voltage before [22–25] or after [6, 26–28] the LC-filter, providing a digital representation of the output signal. In [29], one ADC is used to digitize both the input and the feedback signal after summation. The amplifier in [30] has a signal level dependent mode control scheme that can change the modulation and pulse patterns to save power.

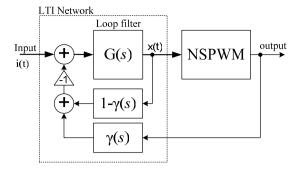

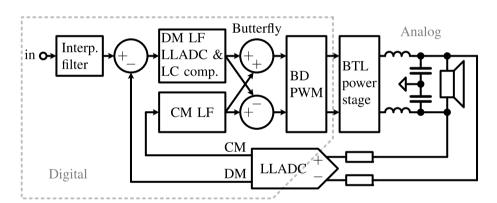

The advantage of applying post-filter feedback is that it allows the amplifier to correct for non-linear effects in the output filter inductor and capacitor. Further processing of the feedback signal can be done in the digital domain where the filters do not suffer from the component spread present in analog filters. A generic representation of a post-filter feedback system is shown in Figure 1.8.

### 1.3.3 Implementations

To highlight the differences in the implementations presented in literature, this section elaborates briefly on each topology.

Figure 1.8: Block diagram of a class-D amplifier with digital post-filter feedback.

### **Before The Output-Filter**

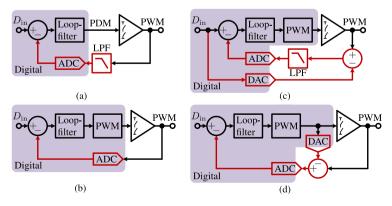

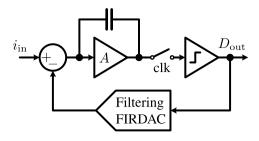

An amplifier prototype using an field programmable gate array (FPGA) board and a commercially available  $\Sigma\Delta$ -ADC was built in [22]. The  $\Sigma\Delta$ -ADC was carefully selected to have a direct bitstream output for minimum delay. Its input is preceded by a 1<sup>st</sup> order low-pass filter to suppress the PDM switching residue of the filter-less output. The simplified diagram of this topology is shown in Figure 1.9a.

Another paper [23] proposes a continuous-time  $\Sigma\Delta$ -ADC tailored specifically for use in Class-D amplifiers with digital feedback. The ADC features inherent 3<sup>rd</sup> order anti-aliasing, allowing it to be connected directly to the filter-less 3-level output stage. The simplified diagram of this topology is shown in Figure 1.9b.

A more recent digital implementation [24] uses a digital-to-analog converter (DAC) to subtract a high-quality noise-shaped copy of the input signal from the output signal to relax the requirements on the feedback ADC. Now, the ADC only has to process the error signal. The simplified diagram of this topology is shown in Figure 1.9c. The amplifier also includes

Figure 1.9: Schematics showing the topological differences of amplifiers with digital input and digital feedback directly after the power stage.

an ADC to sense the supply voltage variations and adapt the required pulse-width of the output accordingly (not shown).

Similar to the implementation in [24], the work in [25] uses a DAC to subtract the PWM signal from the filter-less output signal. Here, the error signal only contains the differences between the DAC and the output of power stage, rather than the full PWM waveform. The simplified diagram of this topology is shown in Figure 1.9d.

### After The Output-Filter

The work of Mouton [6] is, to our knowledge, the first work to present a digital Class-D amplifier with global feedback. A commercially available ADC is used to digitize the voltage after the output filter before feeding it to the fully digital loop filter and modulator. The work also implements a technique to reduce the non-linearity caused by the presence of the PWM ripple residue in the feedback signal and provides a load characterization method.

Both the works in [26, 27] present a digital Class-D amplifier based on a tailor made low-latency ADC (LLADC) to provide feedback after the output filter. The amplifier in [26] is monolithically integrated on a single die, and features a multi-phase output stage. The product in [27] is a highly configurable controller chip that is to be used with an external power stage. This solution is covered in more detail in section 4.3.

Another work presents a multi-phase digital amplifier with global feedback solution based on a fixed-point core signal microcontroller with embedded successive approximation register (SAR) ADC and PWM interfaces [28]. It shows that it is possible to implement such an amplifier with just a microcontroller, significantly reducing the cost with respect to an FPGA or CMOS implementation while still achieving reasonable performance.

These implementations all resemble the architecture of the system in Figure 1.8 with the main difference being the output stage configuration. Output stages will be discussed in the next section and a more thorough analysis of multi-phase systems is presented in chapter 3.

### 1.4 Output stage

In order to deliver power to the load, the PWM signal has to be amplified, hence, a power stage is inserted after the modulator. A basic power stage consists of two power metal-oxide-semiconductor field-effect transistors (MOSFETs) that can switch the output between the high and low supply rail. A driver circuit is required to charge and discharge the gates of the power MOSFETs. Moreover, the driver circuit inserts dead-time to prevent cross conduction preventing the power MOSFETs from breaking down.

Additionally, the driver can implement clip protection. In the following sections, the design choices in a power stage will be considered.

### 1.4.1 Power MOSFETs

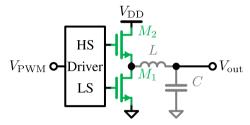

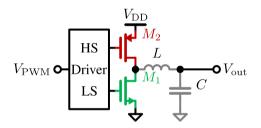

A pair of power MOSFETs forms a half-bridge that is connected to the load via an optional LC low-pass filter. These MOSFETs can either be both NMOS as in Figure 1.10a, or a complementary pair of an NMOS and a PMOS transistor as in Figure 1.10b.

(a) An output stage utilizing 2 NMOS transistors.

(b) A complementary output stage.

Figure 1.10: Commonly used output stages.

The dual NMOS transistor power stage requires a bootstrapped supply to operate the high-side driver, but can use the same driver circuit for the high- and low-side driver. In contrast, for a CMOS implementation the PMOS transistor has to be approximately three times larger to provide the same  $r_{\rm ds,on}$  as the NMOS transistor due to the lower hole mobility. Moreover, the power stage will require a different high- and low-side driver, however a bootstrapped supply is not required.

### 1.4.2 Gate Driver

The gate driver is a circuit that controls the power transistors of the output stage. First the PWM signal has to be level shifted to the voltage domains of the low-side (LS) and high-side (HS) gate drivers. The HS driver specifically requires a bootstrapped supply voltage for an NMOS output device or a local supply voltage with respect to  $V_{\rm DD}$  for a PMOS output device.

A way to implement the gate drivers is by a chain of inverters with increasing drive strength. The final inverter that has to drive the power

transistors is usually designed to have a stronger pull-down than pullup strength (in case of an NMOS) to prevent cross-conduction during switching. Drive strength can also be tuned to achieve faster or slower transients to tune for emissions. Usually, logic is added as well to ensure that one power transistor is off before the other is turned on.

For example, in [31], an adaptive gate driver is designed to avoid reverse recovery. A comparator is used to detect reverse current through the power transistor and waits before turning it off completely until the other power transistor has taken over. This way no current has to flow through the fly-back diodes.

In application where the  $V_{\rm GS}$  is in the same order of magnitude as the  $V_{\rm DD}$ , the losses in the output stage are dominated by charging and discharging the gates of the power transistors. In [32], a mobile class-D power amplifier is designed utilizing dynamic power stage activation. The power stage is cut into slices that can be disabled at low power output to reduce the required charge to turn the power transistors on and off, ultimately reducing the power consumption.

### 1.4.3 Bootstrapping

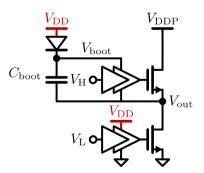

In the output stage as shown in Figure 1.10a the gate of the top NMOS has to be driven with a voltage above the supply voltage to be able to turn it on. At the same time, the driving voltage should also not exceed the maximum rated gate-source voltage. A way to do this, is to either use a charge pump or a bootstrapping circuit, the latter of which will be explained in this section. A commonly used bootstrapping circuit is shown in Figure 1.11.

Figure 1.11: Bootstrap circuit to provide the elevated supply voltage for the high-side gate driver.

When  $V_{\rm out}$  is low, the bootstrap capacitor  $C_{\rm boot}$  is charged to  $V_{\rm DD}$  minus the diode forward voltage. Then, once  $V_{\rm out}$  is switching to  $V_{\rm DDP}$ , it will lift  $V_{\rm boot}$  above  $V_{\rm DDP}$  to provide a sufficiently high voltage to drive the gate of the output transistor.

### 1.4.4 Levelshifting

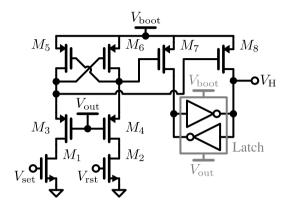

Driving the high-side gate driver requires a levelshifting operation to propagate the low-voltage PWM signal to the bootstrapped voltage domain of the gate driver in front of the output transistor. A basic levelshifter with a latch for a dual NMOS output stage is shown in Figure 1.12.

Figure 1.12: Levelshifter to drive the high-side gate driver.

When the  $V_{\rm set}$  input is high, the gates of  $M_{6,8}$  are pulled down via  $M_3$  which pulls the drains of  $M_{6,8}$  to  $V_{\rm boot}$ . Transistors  $M_{5,7}$  are turned off and the value of  $V_{\rm H}$  is held by the latch to interface with the gate driver in Figure 1.11. Likewise, when the reset input is high, the gates of  $M_{5,7}$  are pulled down which will toggle the latch. Transistors  $M_{3,4}$  are used to limit the voltage swing at the input of  $M_{7,8}$  to the output voltage of the power stage plus one threshold voltage. More sophisticated level shifting circuits which are optimized for speed, efficiency and supply bounce are found in literature [33–35].

### 1.4.5 Dead-time

Dead-time is a period in which both switching devices in the output stage are turned off as shown in Figure 1.13b. Dead-time makes the amplifier more robust by preventing the short-circuit current when the transistors are switching. However, it can deteriorate the THD because it changes the pulse widths of the PWM signal.

Control mechanisms to implement dead-time vary in complexity from a logic gate preventing both transistors to be on simultaneously to a statemachine controlled output stage driver [33]. An approach to eliminate the dead-time as much as possible to reduce distortion is shown in [36]. However, another paper [19] shows that the optimum dead-time for minimum distortion is not equal to zero.

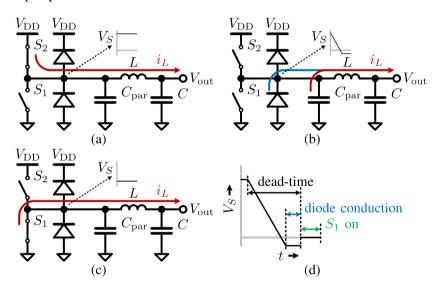

### 1.4.6 Hard- and Soft-switching

Due to the dead-time, the amplifier can utilize soft-switching. Soft-switching is a phenomenon that occurs due to an interaction between the output parasitic capacitance and the filter inductor. The current that starts flowing through the filter inductor in Figure 1.13a is used to charge or discharge the parasitic output capacitance after turning the conducting transistor off in Figure 1.13b. After that, the other power transistor can be turned on while already having zero voltage over its channel as shown in Figure 1.13c, reducing switching losses.

To ensure operation in soft switching, the current through the filter inductor has to change polarity and reach sufficient magnitude during the time a switch is closed. Else it cannot (fully) charge the output capacitance to commutate the output voltage during the dead-time before the power stage switches. This can result in hard-switching or partial soft-switching, which both reduce efficiency. In [37], a tracking loop has been designed which adapts the switching frequency to keep the amplifier in soft-switching. As a result the amplifier achieves a high efficiency at any output power level.

Figure 1.13: Dead-time and soft-switching visualized for a positive output current.

### 1.4.7 Overcurrent protection

A versatile overcurrent protection technique that acts differently for scenarios such as short circuits and load impedance variations is discussed in [38]. The implemented technique is tested to be robust against connecting the output after the LC-filter to the negative or positive supply. The current limiting in normal operation prevents audio holes that are caused by

hiccup limiting in conventional designs. Finally it is possible to use smaller double-diffused MOS (DMOS) transistors in the output stage because they do not have to be over-dimensioned for short circuit scenarios.

In mobile Class-D applications, it is often a problem that the speaker is destroyed by dissipating too much power. In the design in [39], a digital signal processor (DSP) runs a speaker protection algorithm that limits the membrane excursion and voice-coil temperature of the speaker. Furthermore, a battery safeguard that limits the current drawn from the battery when it nears discharge is implemented.

### 1.5 Class-D Non-idealities

The improved efficiency of Class-D amplifiers does come at a cost. The high-voltage switching transients in class-D amplifiers can radiate due to the high  $\mathrm{d}V/\mathrm{d}t$  and  $\mathrm{d}I/\mathrm{d}t$ . The added dead-time to prevent cross-conduction degrades the linearity of the power stage, necessitating the use of a feedback loop or pre-distortion to suppress this non-linearity. Also, the theoretical 100 % efficiency is never achieved due to various loss mechanisms in the amplifier.

### 1.5.1 EMI

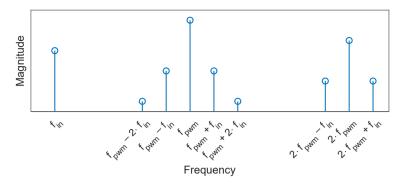

A couple of different phenomena in the Class-D amplifier cause EMI, namely, the switching frequency, its harmonics and intermodulation products, which all reside around the amplitude modulation (AM) radio band. Next, we also have the sharp transitions at the pulse edges and reverse recovery currents, which can excite resonances in parasitic LC loops, causing interference around the frequency modulation (FM) radio band. Interference with other electronic equipment has to be avoided, thus precautions should be taken to make the amplifier adhere to EMI regulations.

### 1.5.2 PWM Ripple

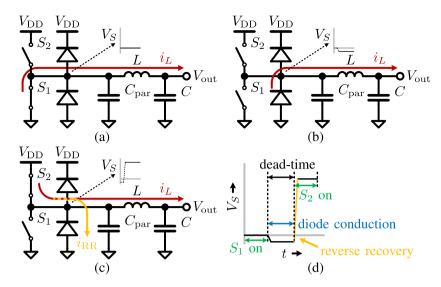

Let's focus on the EMI due to the switching frequency. The small bandwidth between the audio band and the PWM switching frequency allows for limited filtering of the switching frequency components. As a result of this the load voltage still contains a ripple component which is shown in Figure 1.14. When a load is connected through long speaker wires, these wires will act as a parasitic antenna that can radiate the switching frequency components.

The worst kind of excitation is a common-mode (CM) signal, because it excites both wires with the same signal, which is optimal for the wires to work as an antenna. On the contrary, differential mode (DM) signals excite the wires in anti-phase, which gives opposing fields around the wires that cancel most of the radiation. Due to the relatively low frequency of

Figure 1.14: Visualization of the inductor current ripple and load voltage ripple.

this type of EMI, it could be possible to reduce it by means of additional circuitry.

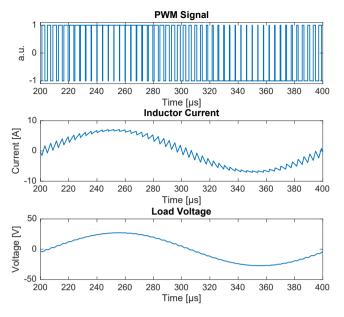

### 1.5.3 Reverse Recovery

When dead-time is applied to the driving signal of a power stage, it is possible to get reverse recovery due to the flyback diodes that are in parallel with the switching devices. Reverse recovery is the charge dump that occurs after the flyback diode stops conducting when the opposite switch is closed. This effect is illustrated in Figure 1.15 for the hard-switching case where a current flows from ground through  $S_1$  and the inductor.

First, the lower switch  $S_1$  is conducting the inductor current as shown in Figure 1.15a. Then, the switch is opened and once the capacitor voltage goes below zero and reaches the forward voltage of the diode, the diode will start to conduct the current in Figure 1.15b. Finally, when  $S_2$  is closed, the voltage difference between this state and the previous state is equalized. The diode stays in a conducting state until the stored minority carriers are fully discharged, resulting in a reverse recovery current  $i_{\rm RR}$  to dump the space charge stored in the diode. This sharp transient can excite ringing in stray inductance from the package and PCB tracks causing EMI. [40, 41]

### 1.5.4 Ringing Parasitics

Both the sharp edges of the pulses and the reverse recovery current can cause ringing of parasitic LC tanks in the output stage. The capacitance

Figure 1.15: Reverse recovery visualized for a positive output current.

originates from the parasitic capacitance of the output transistors and the inductance is due to the wiring and/or lead-frame of the package. Initial research has shown that the frequency of this ringing is in the 10 MHz – 100 MHz range for a discrete output stage with off-the-shelf components. However, there are still mismatches between simulation and measurements that are yet unexplained [42, 43].

### 1.5.5 Dissipation sources

Class-D amplifiers owe their high efficiency to their switching output stage. The output transistor either conducts current without having a voltage drop or sustains the supply voltage without conducting current, yielding a low dissipation in the power MOSFETs.

In [37], the contributions to the power dissipation in class-D amplifiers have been investigated. The main dissipation sources have been listed in Table 1.1.

Table 1.1: List of main dissipation sources in a class-D power stage

| Dissipation type                 | Source                                                                 |

|----------------------------------|------------------------------------------------------------------------|

| Conduction loss $P_{con}$        | $I_{ m out}$ conduction through $r_{ m on}$                            |

| Ripple loss $P_{\rm rip}$        | $I_{\rm rip}$ conduction through $r_{\rm on}$ and inductor core losses |

| Gate driver loss $P_{\rm g}$     | (Dis)charging the gate capacitance of power transistors                |

| Capacitive loss $P_{\text{cap}}$ | (Dis)charging the output capacitance                                   |

| Switching loss $P_{\rm sw}$      | Hard switching losses in the power transistors                         |

### 1.6 Research Questions

As was mentioned in the previous sections, Class-D amplifiers suffer from non-ideal effects. Ideally, we would like to have a Class-D amplifier that can be used like a Class-AB amplifier, which has no EMI problems due to switching and requires less external components. A general set of research questions is presented:

- How can we reduce EMI of Class-D amplifiers due to the PWM carrier frequency?

- How to reduce the amount of external components of Class-D amplifiers?

These questions will be revisited in the next chapter

### 1.7 Thesis Overview

The thesis is organized as follows:

Chapter 2 focuses on potential solutions to EMI in Class-D amplifiers. Different Class-D switching schemes are discussed and how they have an impact on the EMI of the amplifier. Furthermore, an overview of the prior art in EMI reduction techniques is presented.

Chapter 3 gives an elaborate discussion on multi-phase output stage topologies as a possible solution to reduce EMI.

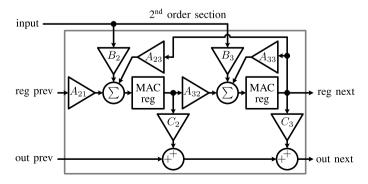

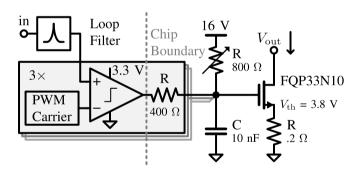

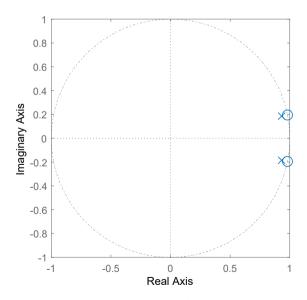

In chapter 4, feed-forward and feedback ripple reduction schemes are discussed to determine their feasibility and the proposed research direction is chosen. Subsequently, it explains the implementation of the Class-D amplifier based around the AX5689 chip which is used as design vehicle to test the ripple reduction technique. Finally, the design of the ripple reduction solution is presented, comprising of a digital loop filter and a Class-A driver connected after the output filter. The amplifier with ripple reduction significantly reduces the power of the fundamental PWM component after the output filter.

Chapter 5 presents the analytical filter design method used in chapter 4 to design closed loop systems with parasitic elements in the loop. This method is used to mitigate the effects of parasitic delays and high-frequency poles when they are a fixed element in the loop. The method has been applied to several different loop filter designs and manages to stabilize them. For low-pass filter design, conventional methods such as reducing the cut-off frequency or gain can also result in a stable filter, however, for band-pass filters this is less trivial. This method also manages to stabilize these band-pass loop filters.

Chapter 6 draws conclusions about the overall thesis and gives recommendations for future research in this field.

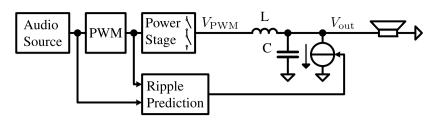

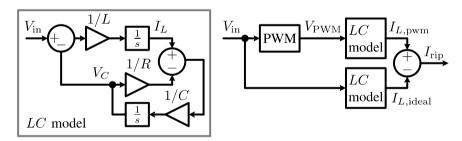

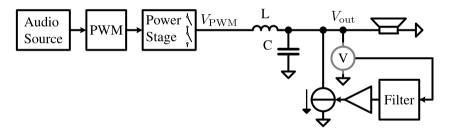

# OVERVIEW OF EMI REDUCTION TECHNIQUES

As discussed in the previous chapter, common-mode PWM ripple is one of the major sources of EMI in class D amplifiers. Therefore, in this chapter, we will investigate techniques to reduce EMI due to the PWM ripple. First the different bridge-tied-load switching schemes of Class-D are shown. Then, the origin of both common-mode and differential-mode EMI at the output of a Class-D amplifier is discussed and an overview of EMI reduction techniques published in literature is presented. Subsequently, the topics of multi-phase and multi-level systems are briefly discussed with a more elaborate discussion on multi-phase systems in chapter 3. Finally, feed-forward and feedback ripple reduction topologies are discussed. The chapter concludes with a motivation for the chosen research questions.

#### 2.1 Prior Art

Several studies have been done to reduce EMI in Class-D amplifiers, for instance in automotive electronics and to allow filterless operation in mobile devices. Three techniques are seen in literature, namely, switching frequency modulation [14, 44, 45], CM modulation [44, 46, 47] and Class-AB/D [48–53]. However, first we will discuss the commonly used bridgetied-load (BTL) power stages, and their effect on EMI.

# 2.2 Bridge-Tied Load

Class-D amplifiers can utilize different modulation schemes [54] when their output stage is in a bridge-tied-load (BTL) configuration as shown in Fig 2.1. Advantages of using a BTL instead of a single-ended configuration are

Sections 2.1 – 2.4 and the 2<sup>nd</sup> paragraph of section 2.10 have appeared in [CEL:3].

Figure 2.1: A BTL output stage.

quadruple the output power using the same supply voltage, no balanced supply requirement, no supply pumping [40], and an improved PSRR [55]. Disadvantages include having to implement the output filter twice, and requiring twice the number of output transistors, the former increasing the cost and the latter increasing system complexity.

The EMI reduction techniques that are explained in this chapter depend on the modulation scheme that is used, hence we will now first discuss these modulation schemes.

#### 2.2.1 AD Modulation

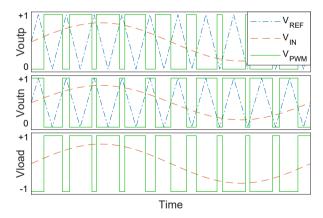

Classical PWM is referred to as AD modulation as shown in Fig. 2.2. In an AD modulated system, the input signal  $V_{\rm IN}$  is compared to the triangular reference  $V_{\rm REF}$  and when the input exceeds the reference in value, a high output level is generated, otherwise a low output level is generated. This output signal is fed to the positive half bridge and an inverted version of it is fed to the negative half bridge.

Figure 2.2: Input, reference and output waveforms as result of AD PWM for a sinusoidal input signal.

Ideally, AD modulation will not excite a CM signal over the load, because the signal is purely differential. In reality mismatch between the LC filters will cause CM to DM conversion of the ripple, because the attenuation in the stop band isn't exactly equal.

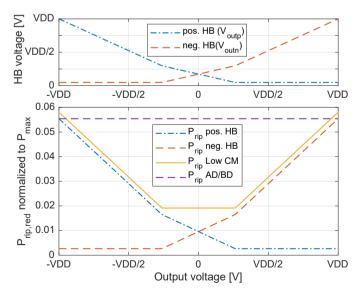

#### 2.2.2 BD Modulation

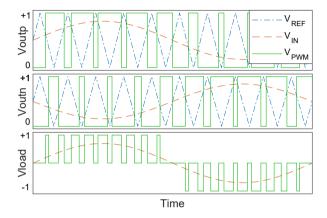

BD modulation takes the same approach for the positive half bridge, however, to generate the negative half bridge signal, the input signal  $V_{\rm IN}$  is inverted before it is compared to the reference  $V_{\rm REF}$  to obtain the PWM signal as shown in Fig. 2.3. In idle this means that there is no DM voltage over the load, however the full PWM ripple is now present in the CM. Using BD modulation effectively doubles the switching frequency which is beneficial for performance.

Figure 2.3: Input, reference and output waveforms as result of BD PWM for a sinusoidal input signal.

Figure 2.4: Input, reference and output waveforms as result of low-CM signaling PWM for a sinusoidal input signal.

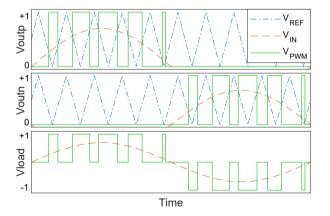

# 2.2.3 Low-CM signaling

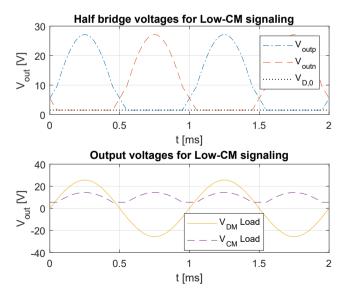

In a low-CM signaling scheme the positive half bridge is responsible for amplifying the positive part of the input signal, and the negative half bridge the other part. This is done by clipping the positive half and the negative half of the input signal  $V_{\rm IN}$  below and above zero, respectively, before comparing them to the reference  $V_{\rm REF}$ , as can be seen in Fig. 2.4.

It is prevalent that this switching scheme excites the CM of the output as only one bridge half is switching at a time. The technique has merits for low-power applications, as the number of switching events is halved compared to AD or BD schemes but does suffer from lower audio performance when compared to regular BD modulation.

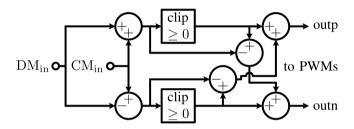

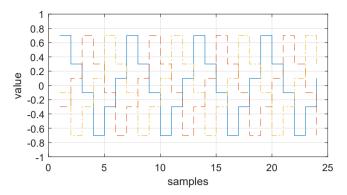

A hybrid implementation that combines low-CM signaling and BD can be used as a trade-off between the performance and power consumption. At lower amplitudes, the idle CM level is not put at 50% duty-cycle but between 5% and 20%. The signals for the modulators can be synthesized using the structure in Figure 2.5 and an example is shown in Figure 2.6.

Figure 2.5: Signal processing structure to synthesize (hybrid) low-CM signaling.

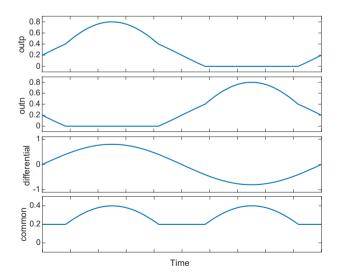

Figure 2.6: Synthesized hybrid low-CM signals and their output DM and CM components.

The DM and CM inputs provide the desired output signal and the desired idle CM level respectively. The clippers limit any signal below zero to zero, after which the excess part is added to the other output signal.

The output is fed to two equal modulators that receive carrier signals ranging from 0 to 1 ensuring that one of the bridge halves is not switching in low-CM mode. If it is also desired to have an elevated output level at that half bridge, such as in chapter 4, the carrier can be set to have a negative lower limit to raise the minimum duty cycle above 0%.

# 2.3 Switching Frequency Modulation

Switching frequency modulation (FM) of the PWM carrier is done by modulating the system clock or the triangle carrier wave. Modulation is done using a triangle pattern in [44], or a uniformly distributed pseudo-random spread spectrum signal in [45] and [14]. These techniques are applicable for both AD and BD modulation.

# 2.4 Common-mode Modulation

CM modulation is a technique that can be applied in BD modulated Class-D amplifiers. Since a zero-output level can be made by pulling both bridge halves to supply or ground, a degree of freedom exists. By randomizing the switching pattern for the zero-output level, the CM power is spread over a larger frequency range and consequently, EMI is reduced. In [44] the randomization is done using a pseudo-random sequence. A more advanced method is used in [46], where the pseudo-random sequence is noise shaped, specifically to have notches around defined AM radio frequencies. Finally the authors of [47] proposed a different BTL topology with two extra transistors to be able to shunt the load accompanied by a 3-level modulation scheme.

# 2.5 Multi-phase

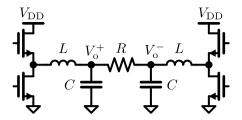

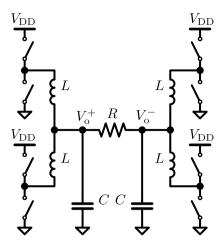

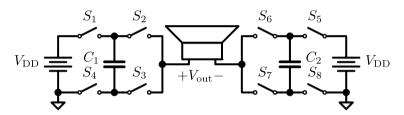

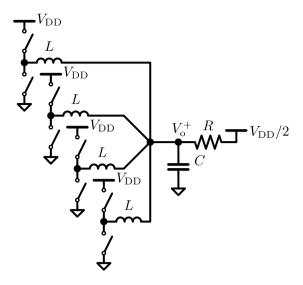

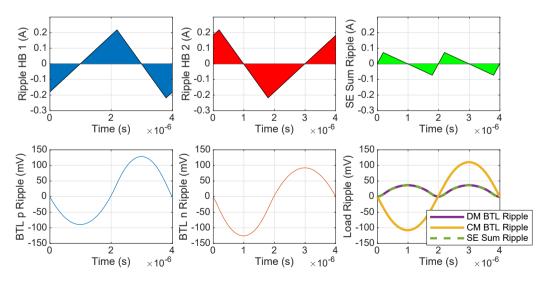

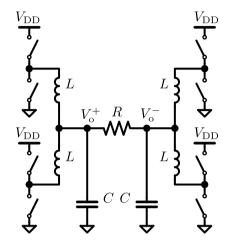

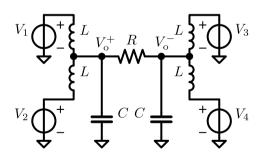

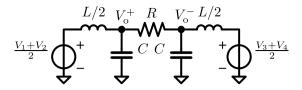

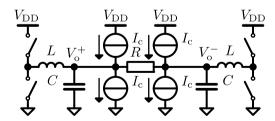

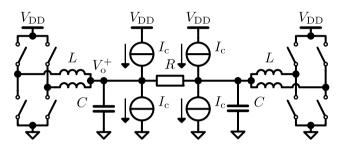

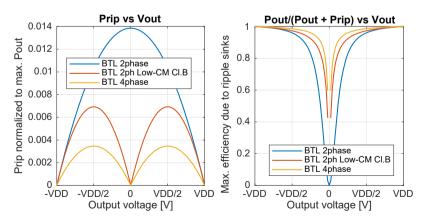

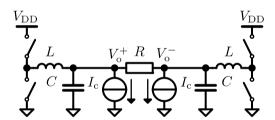

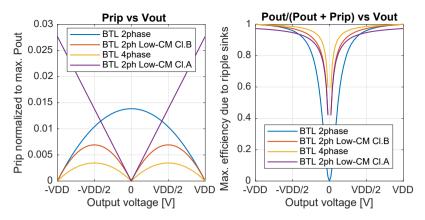

Extending upon the BTL topology, multi-phase output stages have been made. A multi-phase output stage consists of more than two half bridges driving the load either single-ended or in a BTL configuration. Figure 2.7 shows a four-phase BTL system. The parallel inductors at each side sum the current from their respective stages at each side of the load.

The modulation for this kind of output stage is done by using four carriers that are equidistantly spaced in phase. Each carrier is used to modulate the input signal to generate four different PWM signals to drive their respective half-bridge. By using this modulation approach, the ripple voltage over the load is reduced with respect to the ripple in a conventional BTL output stage. As a result the radiated EMI will be reduced. Multi-phase systems and their ripple characteristics will be explored more thoroughly in Chapter 3.

Figure 2.7: A four-phase Class-D output stage.

# 2.6 Multi-level

Multi-level converters are prevalent in the field of high-voltage alternating current (AC) generation which is used in for instance variable speed drives and uninterruptable power supplies. A DC bus voltage is subdivided into smaller voltages by a bank of capacitors. By using switches these voltages can be applied to the load at the output of the converter. Having more levels allows a better approximation of the output voltage because the voltage ripple is reduced.

Multi-level systems can be seen as the dual to multi-phase systems. Where inductors are used in multi-phase systems to sum the output currents, in multi-level systems, capacitors are used to generate different output voltage levels.

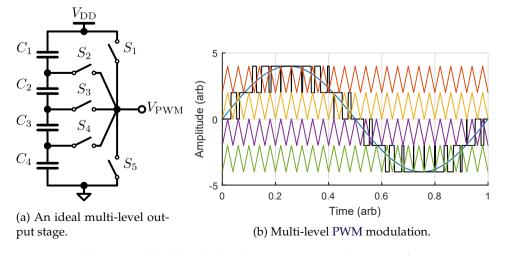

Figure 2.8: Ideal multi-level output stage with its waveform.

An ideal example of a 5-level multi-level converter is shown in Figure 2.8a. A subdivision of the supply is made using four capacitors of equal size to obtain 5 voltage levels that are spaced by a voltage of  $V_{\rm DD}/4$  consecutively. By closing one switch at a time, the corresponding level can be connected to the output terminal. No more than one switch should be closed at a time to prevent short circuiting the capacitors. Hence, a non-overlapping switching scheme should be used.

The modulation for such a 5-level converter can be done by using four offset triangular carriers as shown in Figure 2.8b. The decisions are made by four comparators, resulting in a thermometer coded representation of the input signal. Logic is used to convert the thermometer code to a one-hot code to actuate the switches.

Evidently, since capacitors are used to provide the charge for the inner levels, a way to balance the charges on the capacitors should be implemented. The more voltage levels, the harder it becomes to make a controller that can achieve an acceptable charge balance during operation.

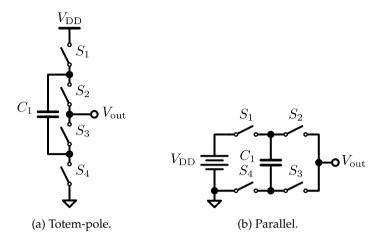

# 2.6.1 Possible Topologies

In literature roughly three different topologies are found to realize a multilevel converter. These three are called the diode-clamped-, stacked Hbridge- and flying capacitor converters [56–58]. In the next sections, each of these converters will be discussed in further detail.

# 2.6.2 Diode-clamped

The diode-clamped structure is shown in Figure 2.9. Like in the ideal converter a string of capacitors is used to make the voltage subdivision. The inner voltage levels are connected to the switches via two diodes, the clamping diodes. These diodes serve as voltage clamps to ensure that the voltage drop over the switches in their off state is equal to or lower than one level. Due to this clamping effect the maximum voltage stress per switch is reduced allowing the use switches with a lower breakdown voltage, saving component costs [59].

The switching sequence of the diode clamped converter will be discussed here. During operation of the 3-level converter in Figure 2.9 two switches are closed while the other two are open. A table showing the three possible switch states is shown in Table 2.1.

Other switch states are not allowed in order to have safe operation, for instance, when switches  $S_1$ ,  $S_2$  and  $S_4$  are closed the voltage stress on  $S_3$  will become  $V_{\rm DD}$  or when switches  $S_1$ ,  $S_2$  and  $S_3$  are closed,  $C_2$  is connected to the supply.

The diode-clamped topology has diodes in the signal path which will cause severe degradation in THD. The diode forward voltage is also significant when compared to the supply of audio amplifiers, reducing

Table 2.1: Switch conditions for a 3-level diode-clamped converter.

| $V_{ m out}$    | $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-----------------|-------|-------|-------|-------|

| $V_{\rm DD}$    | 1     | 1     | 0     | 0     |

| $V_{ m DD}/2$ 0 | 0     | 0     | 1     | 1     |

Figure 2.9: A 3-level diode-clamped converter.

amplifier efficiency. Therefore, the diode-clamped topology is not suitable to make an audio amplifier with good performance.

#### **Equivalent Schematic**

The 3-level diode-clamped converter circuit can be shown in a parallel fashion instead of the totem-pole representation used in most papers. This way of drawing the circuit, shown in Figure 2.10, can more intuitive to understand.

Figure 2.10: Parallel representation of the diode-clamped circuit.

#### More Levels

The diode-clamped converter can be extended to multiple levels by increasing the number of capacitors, switches and diodes. An extra level requires 1 capacitor, 2 switches and 2 diodes, rated appropriately for the voltage they have to sustain. The real challenge in having multiple levels lies in the control algorithm to keep the charges on the capacitors balanced.

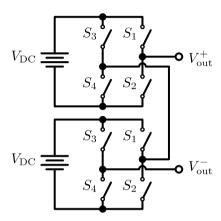

## 2.6.3 Stacked H-bridge

As the name suggests, the stacked H-bridge is a cascade of separate H-bridges. A 5-level converter is shown in Figure 2.11. In order to make this topology work all the direct current (DC) sources should be decoupled from each other to allow stacking of the DC voltages. The possible switch conditions and corresponding output voltages of a single H-bridge are given in Table 2.2

Table 2.2: Switch conditions for an H-bridge.

| $V_{ m out}$  | $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|---------------|-------|-------|-------|-------|

| $V_{ m DC}$   | 1     | 0     | 0     | 1     |

| 0             | 1     | 0     | 1     | 0     |

| 0             | 0     | 1     | 0     | 1     |

| $-V_{\rm DC}$ | 0     | 1     | 1     | 0     |

Figure 2.11: A 5-level stacked H-bridge converter.

By connecting another H-bridge in series it is possible to add or subtract  $V_{\rm DC}$  to the output of the first H-bridge creating two extra levels of  $\pm 2V_{\rm DC}$ . While the idea of this converter looks practical because there are no capacitors required, it does require multiple independent DC-sources. When these are available, which is the case in electric cars with multiple batteries and photo-voltaic systems consisting of several cells, this is a viable converter however in the other cases the use of a stacked H-bridge converter is impractical.

In, for instance, photo-voltaic systems a DC voltage is generated and has to be converted into a 3-phase AC voltage before it can be delivered to the power grid. For this case it is possible to use the stacked H-bridge because the individual supply voltages can be made by grouping photo-voltaic cells.

#### More Levels

By stacking more H-bridges in series, more levels can be generated. Each extra H-bridge adds 2 levels and requires 4 switches and a supply.

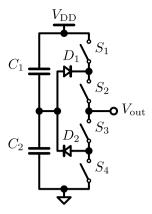

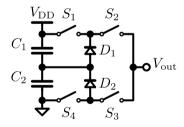

# 2.6.4 Flying capacitor

The third converter that is commonly used is the so called 'flying' capacitor converter. The terminology comes from the fact that neither of the terminals

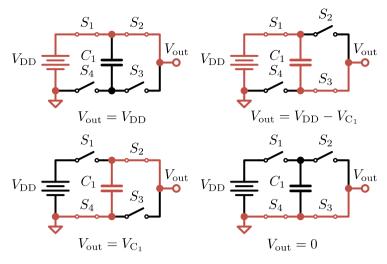

of the capacitors are connected to ground or the supply rail, hence it is floating or 'flying'. A 3-level flying capacitor converter is shown in Figure 2.12. These two representation of the flying capacitor circuit are both commonly found in literature and shown here for completeness.

Figure 2.12: Showing two representations of the same flying capacitor circuit.

The switching conditions for the flying capacitor converter are tabulated in Table 2.3. Here  $V_{C_1}$  is the voltage over the flying capacitor  $C_1$ . By controlling the switch states it is possible to regulate  $V_{\rm C_1}$  to  $V_{\rm DD}/2$  yielding a voltage of  $V_{\rm DD}/2$  for both states in the middle of the table. To do this, the switch states are chosen by a feedback loop in such a way that the flying capacitor is charged or discharged in the direction of  $V_{C_1} = V_{DD}/2$ .

Table 2.3: Switch conditions for the 3-level flying capacitor topology.

| $V_{ m out}$                           | $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|----------------------------------------|-------|-------|-------|-------|

| $V_{ m DD}$                            | 1     | 0     | 0     | 1     |

| $V_{\mathrm{DD}} - V_{\mathrm{C}_{1}}$ | 1     | 0     | 1     | 0     |

| $V_{\mathrm{C}_1}$                     | 0     | 1     | 0     | 1     |

| 0                                      | 0     | 1     | 1     | 0     |

The switch states are illustrated in Figure 2.13 showing all four possible switch states with their corresponding output voltage. The red marked wires indicate the current path to the output referred from the ground.

#### More Levels

As for the other topologies, it is possible to add more levels to the flying capacitor topology. This is achieved by inserting additional parallel capacitors with switches. Each extra section adds 1 level and requires 2 switches and an extra capacitor. Balancing the charges requires increasingly complex

Figure 2.13: Visualized flying capacitor switch conditions.

algorithms to choose the correct combinations for every switching action when the number of capacitors is increased [57].

# 2.6.5 Multi-level Summary

The three most common multi-level converter stages have been discussed. To get an idea of the required components and the series resistance in each topology as function of the amount of subsections, they are conveniently listed in Table 2.4. The assumption here is that all the capacitors are equally

| Table 2.4: | Component re | quirements | at increasing | levels. |

|------------|--------------|------------|---------------|---------|

|------------|--------------|------------|---------------|---------|

| Topology         | Levels | Switches | Caps | Diodes             | DC | Series<br>switches |

|------------------|--------|----------|------|--------------------|----|--------------------|

| Diode clamped    | n+1    | 2n       | n    | $2(n-1)^{\dagger}$ | 1  | $n^{\ \ddagger}$   |

| Stacked H-bridge | 2n + 1 | 4n       | 0    | 0                  | n  | 2n                 |

| Flying capacitor | n+1    | 2n       | n-1  | 0                  | 1  | n                  |

<sup>†</sup> At higher levels, diodes with different breakdown voltages are used.

charged. For the diode clamped and flying capacitors topologies n=1 corresponds to an elementary half bridge, for the stacked H-bridge n=1 corresponds to one H-bridge.

# 2.6.6 Multi-level realizations of audio amplifiers

Multi-level converter systems are commonly used to generate 3-phase outputs for interfacing with the power grid or to make variable frequency

<sup>‡</sup> Also taking series diodes into account.

drives for motor control. It is also possible to operate two converters in 2-phase or BTL mode to drive a loudspeaker. We will focus on applications for audio amplifiers.

The diode-clamped converter is not a good fit for audio amplifiers because of the distortion and efficiency penalty due to the diodes. A stacked H-bridge approach might be usable for an audio amplifier, however the number of required supply rails make it impractical to implement. This leaves the flying capacitor as the most suitable candidate, since it requires a single supply and no diodes.

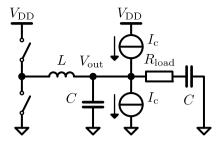

A 5-level audio amplifier has been presented in [60]. Two 3-level flying capacitor converters were used in a filter-less BTL configuration to obtain five discrete output levels. The configuration is shown in Figure 2.14. By doubling the number of components almost twice the output levels are obtained, the exact number is 2N-1 with N the number of levels in a single stage. The flying-capacitor topology is proven to be suitable for implementing an audio amplifier.

Figure 2.14: 5-level BTL flying capacitor implementation.

In both [47] and [61], a 3-level output stage is made by adding a load shunt mode to a conventional BTL output stage. CM EMI is reduced by using an AD switching scheme. Another work utilizing a 7-level output stage with AD switching was presented in [62]. Extra supply voltages are used to provide intermediate levels, which does increase the cost of this application.

# 2.7 Active Ripple Compensation

Class-AB/D is a technique that combines a linear amplifier with a switched-mode amplifier to improve efficiency by delivering most of the power via the switched-mode amplifier instead of the linear amplifier. A feedback loop is built around the linear amplifier to compensate the imperfections, such as distortion and the ripple current, of the switched-mode amplifier. The switched-mode can be controlled by sensing the current of the AB amplifier and using hysteretic control. However, it is difficult to make high loop gain over both the audio band and the PWM frequency range using analog filters while ensuring stability, moreover the AB amplifier will draw a quiescent bias current [49–52].

## 2.8 Feed-forward Cancellation

A feed-forward system that detects and injects an anti-ripple was designed in [63] giving high suppression of both the fundamental and harmonics of the switching frequency. The stationary nature of DC/DC conversion eases characterization of the ripple current, because the output voltage is regulated to be relatively constant. A least mean squares (LMS) algorithm is used to successively approximate the cancellation signal by adding residual errors to it until emission requirements are met or when the hardware limits further optimization. Variations in output voltage, load current and temperature are accounted for by having a look-up table with pre-defined coefficients for those different operation conditions. Suppression ranges from 50 dB at the fundamental to 30 dB at the 20<sup>th</sup> harmonic.

Such a control scheme does not lend itself well for audio applications, as the load voltage and current changes rapidly in contrast to the steady state behavior that is present in DC/DC converters.

# 2.9 Research Questions

In this thesis we would like to reduce the radiated electromagnetic interference from the speaker leads originating from high-frequency switching in a Class-D power stage. A few questions have been formulated around this goal:

- Can the power at the PWM switching frequency after the output filter of the amplifier be reduced?

- Should feed-forward or feedback be used, or a combination?

- How to realize a power efficient implementation with a low component count?

Throughout the research, additional questions have surfaced:

- Is it possible to make an add-on circuit to implement this?

- Can this circuit be implemented using the existing AX5689 IC?

- How can we design loop filters with parasitics in the loop?

#### 2.10 Conclusion

In this chapter we have discussed the mechanism behind EMI after the output filter. The EMI greatly depends on the used modulation scheme and techniques for EMI reduction from prior art have been presented.

The FM and CM modulation techniques result in spreading the power of the interference over a wider band effectively increasing the noise floor. In Class-AB/D a lot of quiescent power is spent to eliminate the ripple in idle conditions, which is bad for efficiency.

The vast amount of components required to make a multi-level output stage compared to a conventional BTL output stage are a disadvantage for making a cost effective solution for consumer electronics. Furthermore, implementations that include diodes will have undesired distortion because of their non-linear signal transfer, making them unsuitable for audio applications. Because of these reasons it was chosen to not further pursue this direction to reduce EMI in Class-D amplifiers.

Extending the flying capacitor topology to more levels will require a sophisticated controller to maintain the charge balance between the capacitors, which could be a topic for further research.

Both the multi-phase and active ripple compensation strategies are candidates for further research and are discussed in more detail in chapters 3 and 4.

# MULTI-PHASE CLASS-D

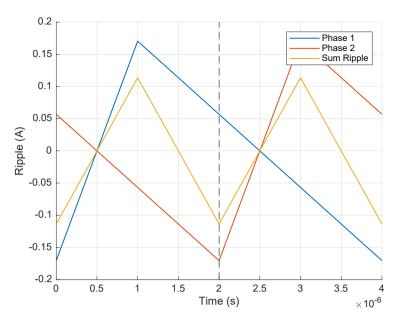

The concept of a multi-phase Class-D amplifier was briefly discussed in the previous chapter. In the current chapter we will dive deeper into the behavior of multi-phase output stages. Note that this chapter provides information on a topic that was explored but later set aside. It is not essential for the next chapters of this thesis. First the current ripple of a single-ended output stage is discussed, followed up by a two-phase system. Subsequently a generalization for any number of phases is shown and the load ripple voltage is determined as well.

Next up, a discussion on output filters is done. The effect of adding phases on the required component values is shown and inductor non-idealities are discussed. Subsequently, by using equations it is shown how quantities such as ripple voltage, ripple current, inductance per leg, stored energy, magnetic field and series resistance are related in systems with multiple phases. Then, a trade-off is presented to show the variation in the aforementioned quantities depending on the amount of phases. Finally the practical issues of implementing multi-phase systems are discussed.

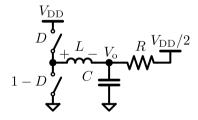

A multi-phase output stage consists of multiple half bridges driving the load either single-ended (SE) or in a BTL configuration. Figure 3.1 shows an example four-phase SE system. The parallel inductors sum the currents from their respective stages at the left side of the load.

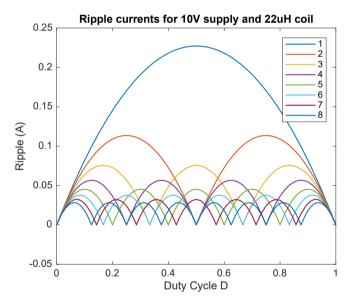

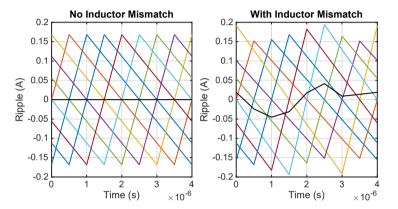

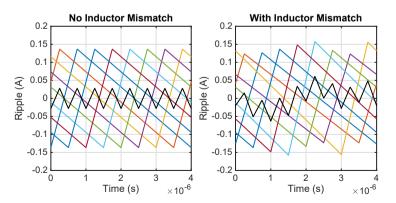

The modulation for this kind of output stage is done by using four carriers that are equidistantly spaced in phase. Each carrier is used to modulate the input signal to generate four different PWM signals to drive their respective half-bridge. By using this modulation approach, the ripple voltage over the load is reduced with respect to the ripple in a conventional BTL output stage. The effect of a multi-phase topology on the inductor and load current ripple is investigated as a lower ripple current generates less EMI.

Figure 3.1: A four-phase Class-D output stage.

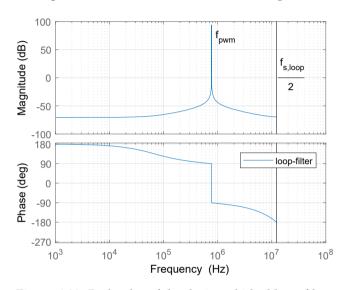

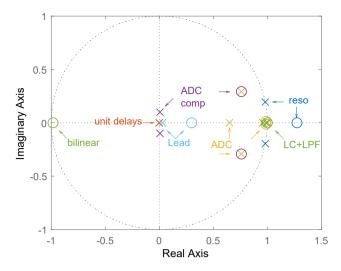

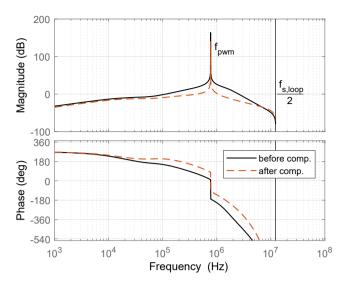

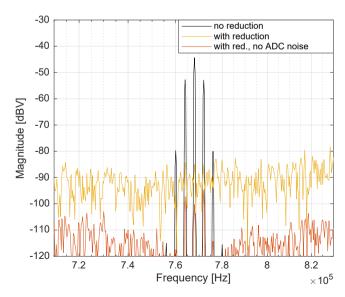

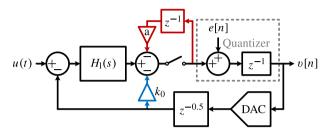

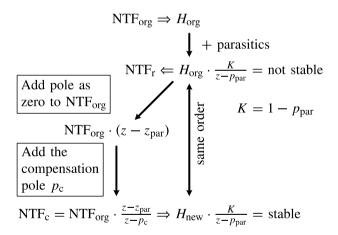

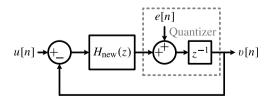

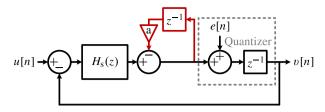

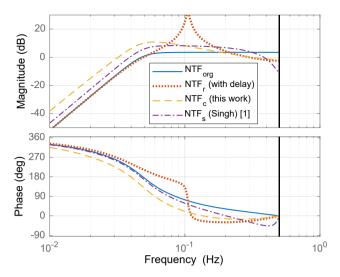

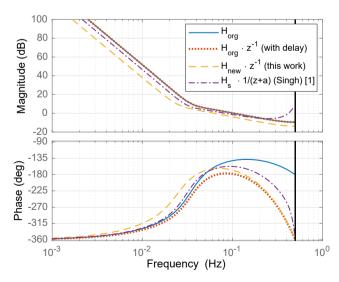

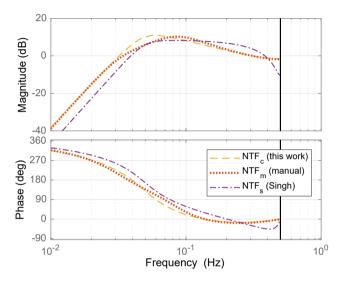

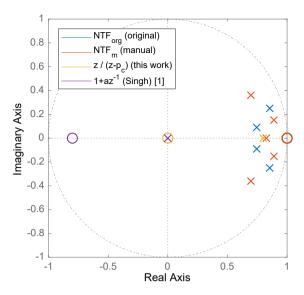

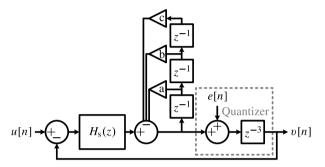

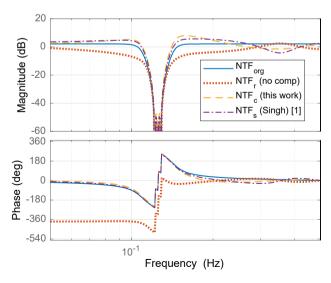

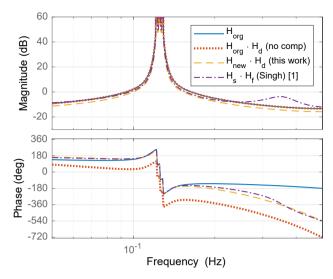

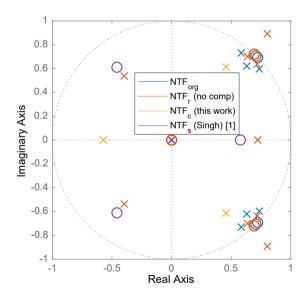

# 3.1 1-phase Ripple Current