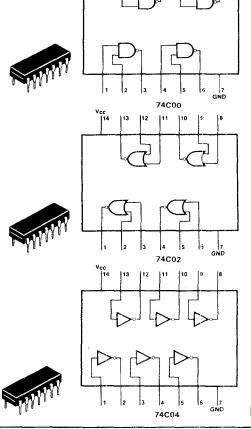

PIN CONNECTION

TOP VIEW

# QUAD TWO-INPUT NAND GATE QUAD TWO-INPUT NOR GATE HEX INVERTER

# GENERAL DESCRIPTION

These logic gates employ complementary MOS (CMOS) to achieve wide power supply operating range, low power consumption, high noise immunity and symmetric controlled rise and fall times. With features such as this the 74C logic family is close to ideal for use in digital systems. Function and pin out compatibility with series 74 devices minimizes design time for those designers already familiar with the standard 74 logic family.

All inputs are protected from damage due to static discharge by diode clamps to  $V_{\rm GC}$  and GND.

# **FEATURES**

- Wide supply voltage range 3.0V to 15V

- Guaranteed noise margin 1.0V,

- High noise immunity 0.45 V<sub>CC</sub> typ.

- Low power consumption 10 nW/package typ.

- Low power TTL compatibility fan out of 2 driving 74L

# ABSOLUTE MAXIMUM RATINGS

| Voltage at Any Pin                       | 0.3V to V <sub>CC</sub> +0.3V |

|------------------------------------------|-------------------------------|

| Operating Temperature Range              |                               |

| Storage Temperature Range                |                               |

| Maximum V <sub>CC</sub> Voltage          | 16V                           |

| Package Dissipation                      | 500 mW                        |

| Lead Temperature (Soldering, 10 seconds) | 300°C                         |

# QUAD TWO-INPUT AND GATE

# GENERAL DESCRIPTION

Employing complementary MOS (CMOS) transistors to achieve wide power supply operating range, low power consumption and high noise margin these gates provide basic functions used in the implementation of digital integrated circuit systems. The N and P-channel enhancement mode transistors provide a symmetrical circuit with output swing essentially equal to the supply voltage. No dc power other than that caused by leakage current is consumed during static condition. All inputs are protected from damage due to static discharge by ciode clamps to  $V_{\rm CC}$  and GND.

#### **FEATURES**

- Wide supply voltage range 3.0V to 15V

- Guaranteed noise margin 1.0V

- High noise immunity 0.45V<sub>CC</sub> typ

- Low power TTL compatibility fan out of 2 driving 74L

- Low power consumption 10 nW/package typ

#### ABSOLUTE MAXIMUM RATINGS

| ABSOLUTE MITAIMUM KITINGS                |                              |

|------------------------------------------|------------------------------|

| Voltage at Any Pin                       | 0.3 to V <sub>CC</sub> +0.3V |

| Operating Temperature Range              | 40°C to +85°C                |

| Storage Temperature Range                | 65°C to +150°C               |

| Package Dissipation                      |                              |

| Operating V <sub>CC</sub> Range          | 3.0V to 15V                  |

| Absolute Maximum V <sub>CC</sub>         |                              |

| Lead Temperature (Soldering, 10 seconds) | 300°C                        |

|                                          |                              |

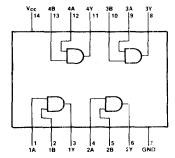

# PIN CONNECTION

TOP VIEW

H = High Level L = Low Level

### TRUTH TABLE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| A      | В | Y      |

| L      | L | L      |

| L      | Н | L      |

| Н      | L | L      |

| Н      | Н | H      |