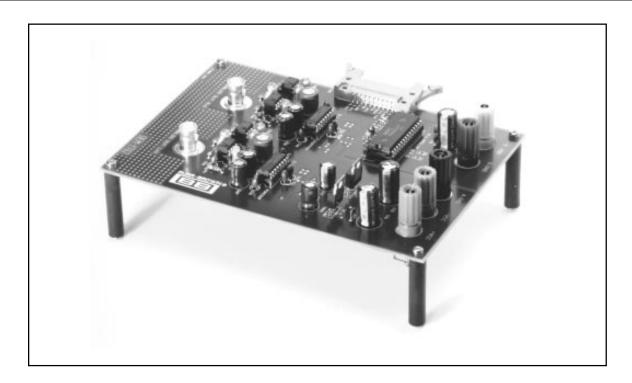

# DEM-PCM1702 EVALUATION FIXTURE

### **FEATURES**

- COMPLETE 20-BIT STEREO D/A CONVERSION SYSTEM

- NEW SIGN-MAGNITUDE DAC: PCM1702P

- 8x DIGITAL FILTER: SM5842AP

- HIGH PERFORMANCE

THD+N at (F/S): 0.0015%

Dynamic Range: 108dB (EIAJ)

S/N Ratio: 120dB (EIAJ)

Non Zero Cross Distortion

- SERIAL DIGITAL INTERFACE

- ANALOG OUTPUT: ±3V

- POWER SUPPLY: ±9V to ±12V, +5V

- DIRECT INTERFACE TO DEM-PCM1760

- BOARD SIZE: 182mm X 128mm

## **DESCRIPTION**

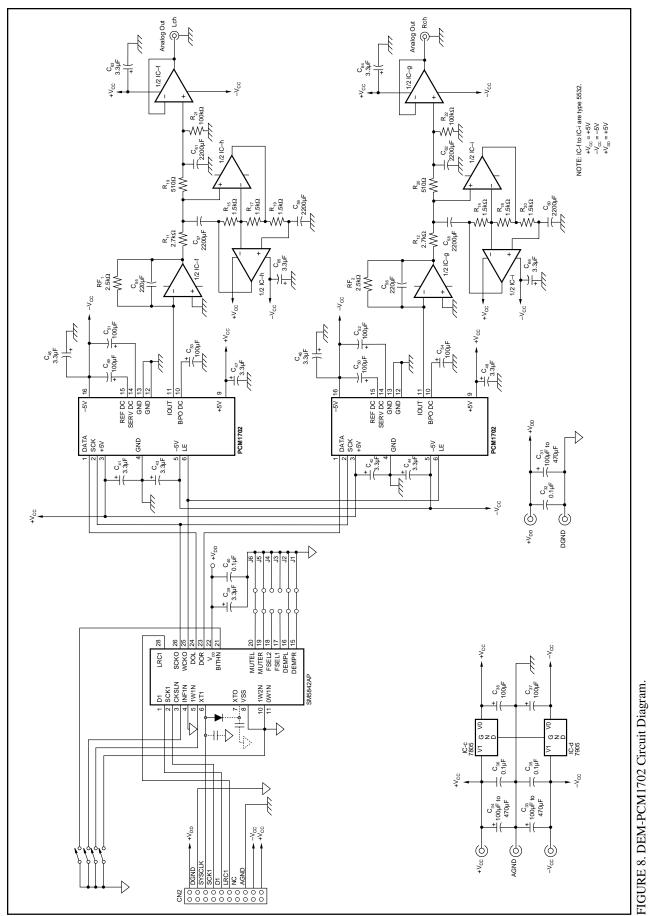

The DEM-PCM1702 is an evaluation fixture for Burr-Brown's sign-magnitude, 20-bit digital-to-analog converter, the PCM-1702. It is primarily intended for quick evaluation of the PCM1702P's spectral purity and sound fidelity.

Two PCM1702s are provided to allow full stereo evaluation. The input to the DEM-PCM1702 can be the output serial data from DEM-PCM1760 (Burr-Brown's evaluation fixture for its 20-bit A/D and digital filter, the PCM1760 and DF1760), or other digital signal source through the interface connector.

The number of digital input data bits and optional functions are selectable by switches on board.

The analog output signal is filtered by a GIC type low pass filter (dual OP AMP) and the filtered output appears on the output connectors (BNCs).

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (602) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (602) 889-1510 • Immediate Product Info: (800) 548-6132

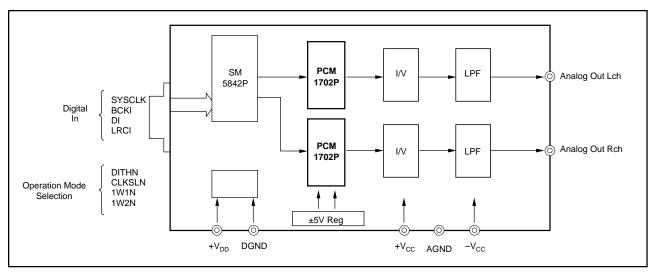

FIGURE 1. Block Diagram of the DEM-PCM1702.

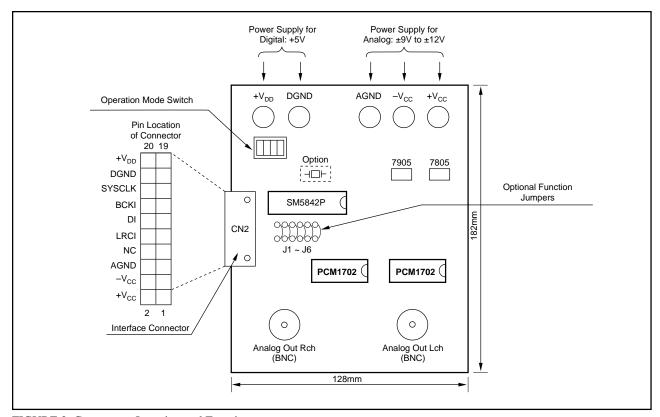

FIGURE 2. Component Location and Function.

#### **OPERATION MODE SELECT SWITCH**

The Operation Mode Select switch provides for the selection of dither, system clock and input format as described in the tables below.

| NAME      | FUNCTION            | L              | Н          |

|-----------|---------------------|----------------|------------|

| DITHN     | Dither Select       | Dither On      | Dither Off |

| CLKSL     | System Clock Select | 256fs          | 384fs      |

| 1W1N (2N) | Input Format Select | Table of Below |            |

| INPUT FORMAT                       | 1W1N | 1W2N |

|------------------------------------|------|------|

| MSB First, Right-justified, 16-Bit | Н    | Н    |

| MSB First, Right-justified, 18-Bit | L    | Н    |

| MSB First, Right-justified, 20-Bit | Н    | L    |

| MSB First, Right-justified, 24-Bit | L    | L    |

For detailed timing infomation, see the data sheet for the NPC SM5842AP.

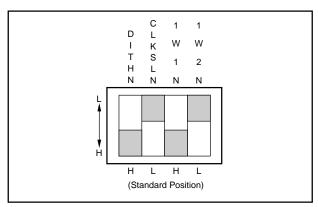

From the factory, these switches are set to provide for no dither, system clock equal 256fs and data format set for MSB first, right justified, 20-bit, as shown below.

FIGURE 3. Opearation Mode Select Switch.

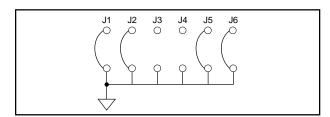

#### **OPTIONAL FUNCTION JUMPERS**

The optional functions of right and left channel de-emphasis, the de-emphasis system clock, and right and left channel mute are controlled by jumpers J1 through J6 as shown in the following table.

| JUMPER # | FUNCTION                | JUMPER  | NO JUMPER |

|----------|-------------------------|---------|-----------|

| J1       | De-emphasis, Rch        | OFF     | ON        |

| J2       | De-emphasis, Lch        | OFF     | ON        |

| J3       | De-emphasis, fs-32kHz   |         | X         |

| J4       | De-emphasis, fs-32kHz   |         | X         |

| J3       | De-emphasis, fs-41.4kHz | Х       |           |

| J4       | De-emphasis, fs-41.4kHz | ×       |           |

| J3       | De-emphasis, fs-48kHz   | ×       |           |

| J4       | De-emphasis, fs-48kHz   |         | X         |

| J5       | Mute, Rch               | No Mute | Mute      |

| J6       | Mute, Lch               | No Mute | Mute      |

From the factory, Jumpers J1, J2, J5 and J6 are installed, as shown below, setting the system clock at 32kHz, no deemphasis and no mute.

FIGURE 4. Optional Function Jumpers.

#### SYSTEM CLOCK OPERATION

A system clock (SYSCLK) is required for operation of the DEM-PCM1702. If the DEM-PCM1702 is being used with the DEM-PCM1760, the 256fs or 384fs system clock is provided by the DEM-PCM1760 through pin 16 of the Interface Connector, as described below. (NOTE: Care must be taken to insure both boards are set to the same master clock.)

If the DEM-PCM1702 is being used where it must generate the 256fs or 384fs master clock, the appropriate crystal can be connected to the SM5842.

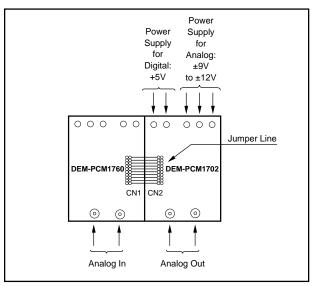

#### **COMBINATION WITH DEM-PCM1760**

The DEM-PCM1702 can be directly combined with the DEM-PCM1760 (20-bit stereo A/D conversion system).

In this case, the connector pins of the DEM-PCM1702 and the DEM-PCM1760 are connected directly together.

The power supply for the DEM-PCM1760 is provided by the DEM-PCM1702 and the serial digital data (within system clock) is provided to the DEM-PCM1702 from the DEM-PCM1760.

FIGURE 5. Combination with DEM-PCM1760.

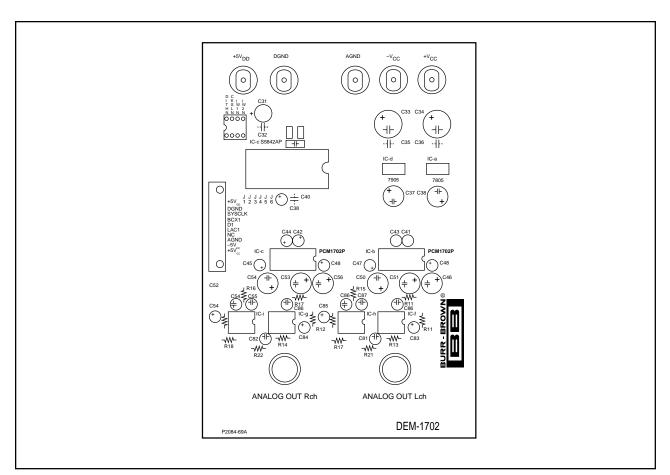

FIGURE 6. DEM-PCM1702 Board Layout and Component Location.

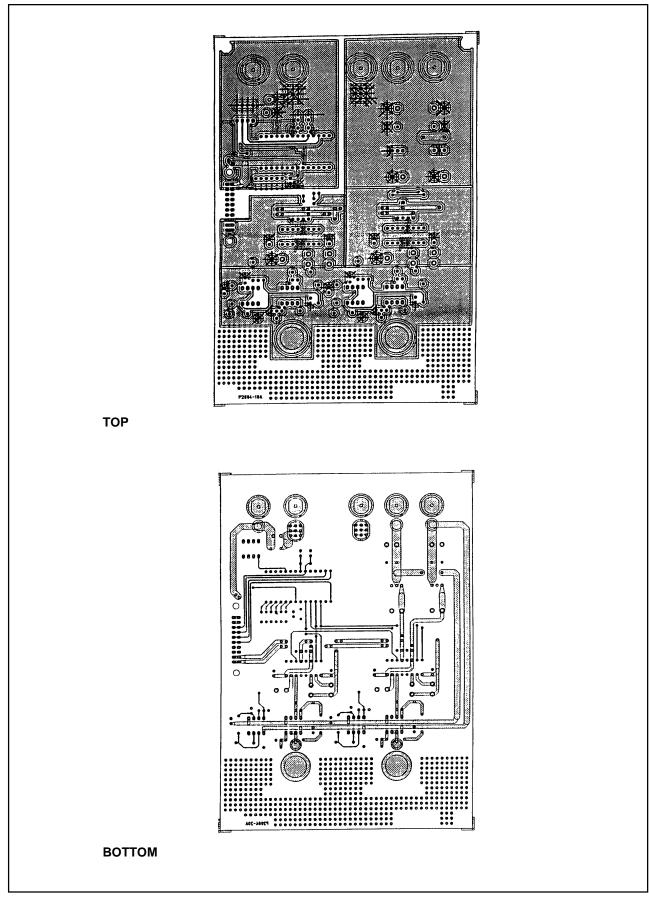

FIGURE 7. DEM-PCM1702 Layer 1 and Layer 2.

BURR-BROWN®

DEM-PCM1702P

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated