- ЦИФРА: реализована в FPGA.

SPDIF-(optical, coaxial) 44100-96000 Hz Мастерклок полностью отвязан от SPDIF через FiFo, что убирает джиттер SPDIF.

USB - 44100-384000 Hz.

В ПЛИС реализовано 8 мультиплексированных FIR c разными коэффициентами интерполяции:

44100х8

48000х8

88200х4

96000x4

176400x2

192000x2

352800x1

384000x1

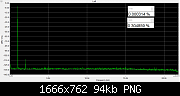

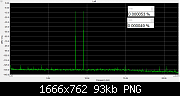

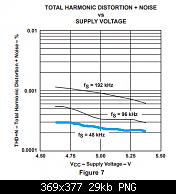

Данный набор FIR обеспечивает работу ЦАП в режиме Fs - 352,8\384,0 KHz не зависимо от входного аудио-потока, что дает минимальные искажения во всем диапазоне Fs (441.1 - 384 KHz). ЦАП работает в режиме кривой на 44,48

- АНАЛОГ: Два моно модуля на PCM1974 в режиме Direct Stream Digital, На борту имеется усилитель для наушников с аттенюатором на реле.

- УПРАВЛЕНИЕ: Управление ЦАП может осуществляться через энкодер либо пультом ДУ. Из основных функций - выбор цифрового входа (коаксиал-оптика), управление аттенюатором на реле, выбор аналогового выхода (наушники - РСА), управление фильтрами и GAIN в цифре, др..

Характеристики, схемы и параметры со временем буду добавлять.

Социальные закладки