Последний раз редактировалось tomtit; 29.05.2013 в 02:03.

В микросхемах - оно конечно да ... но я-то про дискретную схемотехнику говорил .

Про абсолютную точность среднего не понял. Зачем нам его абсолютная точность? Главное чтобы относительно максимального уровня это была ровно половина.

Может имелось ввиду дрейф выходного смещения из-за дрейфа гейна опорника? Так это вроде не проблема: прецизионные резисторы (или сборка) + прецизионный ОУ для формирования отрицательного смещения. А если заморочится, то можно и интегратор сделать.

BD как правило, делают не для аудио, а для управления чем-то с большим динамическим диапазоном по постоянному току или для обратной связи в сигма-дельта АЦП. И там точность "нуля" часто очень критична, нужны миллионные и десятимиллионные доли от шкалы, причем в диапазоне температур и в серии. Никакие "вычитания среднего" этого не обеспечат, только наличие настоящего ноля.

Повозившись с сигма-дельтами, решил посмотреть,

как можно применить цифровые технологии в

народном хозяйстве. Например на мелкой плисине

можно сделать очень качественный, чисто цифровой ККМ для ИИП.

Тактовая частота нужна всего лишь 3.072МГц.

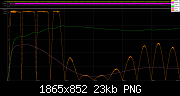

Вот работа его цифровой модели. Показан

процесс зарядки конденсатора 680мкф до напряжения 375В.

Подключена также активная нагрузка 300вт.

Напряжение - зеленая кривая (1:100),

Ток, пропущенный через ФНЧ 10кГц - оранжевая (1:1)

Думаю лучше продолжить в данной ветке.

Да, уже начинаю догадываться. Попробовал замоделить этот модулятор.

У него для работоспособности входной уровень приходится ослаблять где-то на 7дБ, иначе уходит в разнос. Если брать ближайшее значение кратное 2^N, то надо ослаблять в 4 раза, т.е. 12дБ и получается.

Кстати, как и писал Сергей (sia_2), для этого модулятора на входе достаточно х16 оверсемплинга, выше уже разницы не видно.

Для снижения ВЧ шума?

Для этого надо уметь проектировать цифровые фильтры.То что я замоделил - это можно сказать на ощупь.

Если стандартную топологию сумматор-интегратор-квантователь интуитивно еще могу рассматривать как усилитель с нелинейным выходом, то более сложные - не соображу. Только начал вникать в вопрос.

Нет шум не снизишь, а искажения можно задавить глубокой ОС. Для малобитного выхода точность увеличивается за счёт усреднения большого к-ва различающихся отсчетов - отсюда ВЧ шум, он принципиален, если его нет или не хватает, его добавляют искусственно, как дизеринг. Для устойчивого сигма-дельта модулятора выход квантователя болтается примерно +-4 МЗР вокруг истинного значения.

Для однобитого модулятора это означает 4 полных размаха перед квантователем, отсюда эти 12дБ. По этой же причине я считаю, что реальный выигрыш от многобитности начинается с 3-битного выхода.

Последний раз редактировалось tomtit; 21.08.2022 в 23:33.

И да, и нет. Тема на самом деле "многомерная", а что касается коэффициента модуляции - он в однобитнике ограничивается не амплитудными, а временными соотношениями: индекс модуляции 0.8 означает, что модулятор должен сохранять устойчивость, когда выход образован девятью битами одного знака подряд и одним противоположным, то есть эффективной задержкой в петле примерно пять тактов. Тот сониевский модулятор, код которого я приводил, если мне не изменяет склероз, имеет границу устойчивости при гладком входном сигнале около 0.7, и около 0.6 при ступенчатом. Так что там должно быть достаточно 6 дБ (1 бит сдвиг). Опять-таки, если мне не изменяет склероз. Мультибитный же модулятор как раз и позволяет уйти от появления большой задержки в петле с ростом индекса модуляции и тем самым позволяет увеличить глубину обратной связи. Эффект хорошо заметен даже при переходе от двух уровней к трем или четырем, предел отношения сигнал/шум у четырехуровневого модулятора при оверсэмплинге 64 получается почти на 20 дБ выше, чем у однобитника (а не на 6 дБ, как казалось бы на первый взгляд).

Так тот что я моделил (что по ссылке) это он и есть.

Похоже, что 6дБ все таки не хватает. На 20к сигнале работает, на 10к через несколько сек. срывается, на 1к сразу в срыв. И вылазит 3-я гармоника. А если еще плюсовать шум, то вообще без шансов.

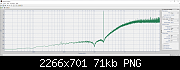

При -12дБ на входе все стабильно и чисто (с большим запасом, т.к. хватает чуть больше 6дБ). 20к сигнал с х16 оверсемплингом на входе:

То же самое на 4-х уровневом квантователе (точнее 5-ти, если считать нулевой):

Последний раз редактировалось dortonyan; 22.08.2022 в 10:11.

Что-то странное. И у Сони, и в одном из моих проектов он точно работал со сдвигом на 1 бит, как в коде, значит ошибка или у меня при выдирании и упрощении кода (упрощение состояло во введении простого округления при сдвигах вправо вместо корректного дитеринга) или в тестбенче. Я специально проверю это в ближайшее время.

Для однобитников, кстати, есть простой экспресс-тест устойчивости - квазипостоянный сигнал, типа очень медленной пилы или синуса, в этом случае то место, где он начнет сваливаться - и есть практический предел (для более высокочастотного сигнала предел устойчивости как правило, выше).

Понятно. Я шум добавлял минимальной амплитуды (+/-0.5LSB), чтобы спектр шума не зависел от сигнала. А для линеаризации DNL надо видимо побольше (чтобы соседние семплы перемежались). Как-нить попробую.

---------- Сообщение добавлено 11:26 ---------- Предыдущее сообщение было 11:22 ----------

Я с кодом не сверялся, лень. Возможно у меня в модели что-то некорректно сделано. Т.к. на 6дБ на 20к работает, только с понижением частоты начинаются глюки.

Ну и если чуть больше 6дБ ослабление делать, то тоже порядок (т.е. если входной сигнал домножить не на 0,5, а на 0,49). Т.е. 6дБ у меня получается где-то на грани.

---------- Сообщение добавлено 11:43 ---------- Предыдущее сообщение было 11:26 ----------

Ну так на этой частоте надо же не одну операцию выполнить, а несколько десятков. И каждая операция может занимать не один такт процессора, а несколько. Вот и считайте.

У обсуждаемого выше соньковского модулятора такая же частота, но на проце это будет может и проще (хотя кому как), но дороже и с потреблением как минимум на порядок больше (скорее на полтора порядка, хотя конечно зависит от выбранной плисины).

В принципе если реализовать только цифровой канал по напряжению, то можно обойтись и микроконтроллером. Но ККМ содержит ещё петлю слежения за током, там нужно обрабатывать поток примерно 768к 12бит отсчетов в секунду для управления 5-битным ШИМ. Тут уже сложнее, нужен DSP или ПЛИС. Конечно, это справедливо только для мощных высокоэффективных ККМ в режиме непрерывного тока. Для простых ККМ, в граничном режиме или с разрывным током дросселя токовая петля не нужна вообще.

От сложности математики зависит само собой, я к тому что у проца 72мгц будет почти 90 тактов на 1 отсчёт при 768к, что-нибудь можно успеть посчитать

Если арм, то слабо верится, можно для спортивного интереса дизассемблером глянуть, но на моей памяти они не выполняют одну инструкцию за такт, плюс нужно время на переходы

_________________

Евгений

Есть АРМы заточенные под ККМ, они точно успеют. Цена АЦП около 2$. Цена ПЛИС iCE40UP5K около 10$ с встроенной флэшкой вполне конкурентноспособна с МК. И их можно купить в отличие от. А для машины более 1кВт эта цена вообще не видна на фоне цены даже входного сетевого фильтра.

Последний раз редактировалось tomtit; 22.08.2022 в 19:39.

Последний раз редактировалось dortonyan; 22.08.2022 в 20:24.

Я тоже постил модулятор от Сони здесь

https://forum.vegalab.ru/showthread....=1#post2883906

и даже версию АЦП на его базе. Вроде тоже не видел проблем с сигналами ниже -6дВ.

Можно, наверное прямо с картинок перенести модель в LTspice и проверить.

Я подсел на другой, коммерческий симулятор, но вроде бы LTspice тоже поддерживает смешанные аналог/цифра проекты.

Так у меня проблема когда сигнал на входе наоборот - выше (или равен) -6db относительно размаха на выходе однобитного квантователя.

---------- Сообщение добавлено 21:06 ---------- Предыдущее сообщение было 21:01 ----------

Кстати, обнаружил что при изменении уровня сигнала меняется вид шумовой полки. Такая корреляция не добавит искажений на ФНЧ?

---------- Сообщение добавлено 23.08.2022 в 15:57 ---------- Предыдущее сообщение было 22.08.2022 в 21:06 ----------

Попробовал упростить соньковский модулятор. Урезал порядок до 3-х. Взамен повысил оверсемплинг до х256 (из расчета использования 512Fs тактовых генераторов). Частота семплирования сигнала на входе при этом х32.

Сделал скважность бита 50% и перекрестно дифференциально-симметричный выход (как в dsd1700):

Нефильтрованный спектр на 20кГц сигнале:

Входы верхнего осциллоскопа:

А затем решил проверить, что же будет на выходе I/U конвертера при условии добавления фильтрации (емкость в ООС параллельно резистору IU). Для модели добавил на выход бессель 1-го порядка с частотой срез 50кГц:

Получается такой выход:

Сигналы с нижнего осциллоскопа:

Если растянуть развертку, получается видна ступенька дискретного сигнала, скорость нарастания которой ограничена фильтром:

Данный сигнал взят с выходного сумматора, но на выходах ИУ то же самое вдвое меньшей амплитуды.

Так вот, если пересчитать сигнал к размаху на выходе I/U 2V rms, то получается, что скорость нарастания сигнала на выходе ОУ получается в районе 8 в/мкс! Т.е. вроде бы ужас, ужас - однобитный выход, помехи и все такое. А на деле, если каскад фильтрации делать прямо в каскаде I/U (даже не MFB, а просто емкость в ООС), то достаточно менее 10 В/мкс линейной скорости нарастания ОУ. Конечно полоса нужна хорошая, как у AD797, LT1468, ADA4896 и т.п. Но на худой конец можно обойтись и чем-то вроде 5534.

И нафига, спрашивается, заморочки с мультибитными модуляторами и аналоговыми FIR-ами? Для формальных цифр SNR или THD+N в широкой полосе?

SNR и упрощение проектирования. Чтобы уйти от большого OSR, ограничившись 64, в крайнем случае 128.

Социальные закладки