Последний раз редактировалось tomtit; 29.05.2013 в 02:03.

Там как раз прямоугольное окно и разброс резисторов не имеет значения - это не DEM,

а усеченный по габаритам и частоте клока вариант ШИМа Бруно.

Для этого модулятора лучше всего подходит простейшая структура из цепочки интеграторов с распределенной ОС.

Такой модулятор имеет передаточную х-ку ФНЧ высокого порядка и считается за 1 клок на выборку, что немаловажно при такой высокой тактовой.

Коэффициенты все одно-битные, умножителей нет.

Есть некоторые издержки - один аккумулятор должен быть > 32 бит, если не идти на небольшие компромиссы.

Offтопик:

Спасибо! Теперь найти бы время на реализацию в железе.

Примерно так же, но сам узел D-A получается намного капризнее и проблемнее из-за гораздо большей доли ВЧ помех.

Ну вот, переписал модель на Verilog и проверил весь цифровой тракт 44.1к->DSD1024+AFIR.

Поправил парочку очень маленьких ошибочек - убрал DC смещение ~0.1% шкалы, и сделал АФИР на 8 отводов.

Выкладываю еще парочку картинок 19к @ 44.1, но это уже после Verilog симуляции всего тракта.

Прекрасно видно шум 16-битного квантования входного синуса и первый алиас от 19к.

FFT - очень длинный 2**20, чтобы увидеть все возможные гармоники и спуры.

Разрешение окна -140дБ, поэтому пик расширяется книзу.

Последний раз редактировалось tomtit; 16.04.2020 в 21:33.

Выглядит очень интересно, там -100 дБ на 100к, вообще супер. Все что выше 100к уже аналог отфильтрует. Очень интересно было б на код посмотреть...

На однобитном модуляторе при той же тактовой можно отодвинуть начало нарастания шума до ~170кГц.

На практике приходится делать возврат к нулю для борьбы с ИСИ, поэтому частоту выхода модулятора приходится уполовинивать

и рабочая полоса будет ~85кГц, то есть все уже скукожилось вдвое. Потом еще и AFIR тоже надо сделать в 2 раза длиннее.

А главная проблема, что все ошибки в аналоговых ключах пропорциональны частоте их переключения, которая в случае ШИМа на порядок ниже.

Ну и напоследок - дизеринг модулятора на картинке - 2ТПДФ, что напрочь убирает всякие модуляции шума и прочие вредные вещи.

С одно-битными модуляторами надо, видимо, делать выход с пассивным диплексером.

Диплексер имеет почти активный входной импеданс и не затягивает переходные процессы в нелинейных ключах.

Проблема - в изрядном количестве качественных катушек с высокой SRF.

Последний раз редактировалось tomtit; 16.04.2020 в 21:47.

tomtit, красиво! А переходную характеристику можно показать?

транзисторный однотакт любой модификации -это масло сливочное (с) FEDGEN

Будет ли это в железе реализовано?

Несмотря на то, что подход Бруно Путзейса показывает приличные результаты, я все-таки считаю его дизайн не слишком оптимальным.

Вот, что можно получить с ДСД512 с тактовой вдвое ниже (1024х), используя дифференциальный АКИХ длины 32(64 с учетом дифф.) с одинаковыми резисторами.

Видно только 3-ю гармонику на уровне -170дБ, и это на сигнале 0дБ! Максимальный допустимый уровень сигнала ~0.75.

Подавляющего преимущества мультибитного ШИМ SDM что-то не видать.

Последний раз редактировалось tomtit; 19.04.2020 в 19:30.

То бишь цифровое усиление минус 2,7 дб. А запас на ИСИ? И насколько вырастут искажения на реальном железе? А вообще очень впечатляет, да и душа больше лежит к 1 бит . Кроме того, резко снижены требования к постфильтру.

Картинка чисто иллюстративная, выход показан без нормировки, в условном цифровом коде, реальный коэффициент передачи аналога где-то около 1/4.

Ухудшение спектра и потеря 50% частоты клока на ИСИ учтены.

Для компенсации вредных свойств однобитного модулятора необходимо делать, как минимум, усреднение по 4 отсчётам.

Тогда убирается эффекты RZ и огромная палка на частоте Найквиста для малых амплитуд вх.сигнала.

Требования к пост-фильтру снижены только из-за сдвига "шумовой стенки" вправо примерно до 87кГц, то есть, в точности то же, что и у Бруно.

В Мола-Мола он обходится фильтром 3-4го порядка.

Но! Не хочется городить монстра из 64 резисторов на канал, как в оригинале, это пусть радиолюбители попробуют.

DSD512 можно сгенерировать чисто программно и вывести через какую-нибудь готовую USB примочку.

То есть я хотел сказать, что если удалось сделать удачный АКИХ длиной >= 32, то всё остальное становится не критичным.

Особенно, если не заморачиваться в отношении SNR, который то и нужен почти только для рекламы.

P.S.

Ну и насчет ресурсов FPGA для урезанного Мола-Мола 1024x - это < 75% XC6SLX9-2TQG144C, проверено, влезает с нулевым тайминг скором.

Включено всё - от входа SPDIF до выхода ШИМ.

Последний раз редактировалось tomtit; 20.04.2020 в 18:59.

Offтопик:

Нашел не очень разумное объяснение такому странному ДФ в Мола-Мола.

Если Бруно сделал одноступенчатый интерполятор *16 или *32 для 44.1,

то длина КИХ будет намного больше 1000, если задать подавление на частоте Найквиста ~ 20дБ

и обеспечить достаточно гладкую АЧХ в звуковой полосе.

Стандартный алгоритм Паркс-МакКлелана обычно начинает изрядно глючить на таких длинных фильтрах.

Тут он наверное решил, что и так сойдет.

Последний раз редактировалось tomtit; 22.04.2020 в 16:56.

А поподробнее? И так ли уж референсно решение Mola, наверняка он столкнулся с неразрешимыми компромиссами и предпочел ничего не делать , а оставить как есть. Главное- обьявить про 150 дб SNR, чтобы люди понесли свои гульдены , а дальше война план покажет.Он ,кстати , зря затеял дискретные ОУ, они конечно лучше Burson-a, но не фонтан, если серьезно. Так что Бруно можно верить только до границы SDM и фронтэнда.

Последний раз редактировалось vladimir sim; 20.04.2020 в 19:51.

Offтопик:

Конечно гульдены - это святое. Но Бруно еще и романтик в некотором роде.

Дискретные ОУ он замутил для дифф. входа NC400, который принципиально

весь дискретный идеологически. В ОЕМ изделиях он их не применяет.

В оправдание он сказал, что там где нужен высокоомный неинвертирующий вход,

даже лучшие LME искажают слишком сильно из-за большой нелинейной входной емкости.

Тогда он добавил повторители на малоемкостных бип. транзисторах, а дальше пошло-поехало.

А Вы измеряли его изделия?

---------- Сообщение добавлено 13:32 ---------- Предыдущее сообщение было 13:16 ----------

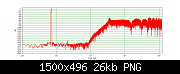

Я пока сделал такие ДФ на х16.

Загиб наверх - компенсация завала в последующем интерполяторе в x64раза.

Последний раз редактировалось tomtit; 21.04.2020 в 01:46.

Социальные закладки